Space engineering

ASIC, FPGA and IP Core engineering

Foreword

This Standard is one of the series of ECSS Standards intended to be applied together for the management, engineering, product assurance and sustainability in space projects and applications. ECSS is a cooperative effort of the European Space Agency, national space agencies and European industry associations for the purpose of developing and maintaining common standards. Requirements in this Standard are defined in terms of what shall be accomplished, rather than in terms of how to organize and perform the necessary work. This allows existing organizational structures and methods to be applied where they are effective, and for the structures and methods to evolve as necessary without rewriting the standards.

This Standard has been prepared by the ECSS-E-ST-20-40C and ECSS-Q-ST-60-03C Working Group, reviewed by the ECSS Executive Secretariat and approved by the ECSS Technical Authority.

Disclaimer

ECSS does not provide any warranty whatsoever, whether expressed, implied, or statutory, including, but not limited to, any warranty of merchantability or fitness for a particular purpose or any warranty that the contents of the item are error-free. In no respect shall ECSS incur any liability for any damages, including, but not limited to, direct, indirect, special, or consequential damages arising out of, resulting from, or in any way connected to the use of this Standard, whether or not based upon warranty, business agreement, tort, or otherwise; whether or not injury was sustained by persons or property or otherwise; and whether or not loss was sustained from, or arose out of, the results of, the item, or any services that may be provided by ECSS.

Published by: ESA Requirements and Standards Section ESTEC, P.O. Box 299, 2200 AG Noordwijk The NetherlandsCopyright: 2023© by the European Space Agency for the members of ECSS## Change log

|

ECSS-E-ST-20-40C

|

First issue

|

Introduction

Developing custom designed monolithic integrated circuits such as ASICs or FPGAs, and developing IP Cores, as off-the-shelf Building Blocks for these complex ICs, make certain engineering and technical management activities crucial to the success of these developments.

ECSS-E-ST-20-40 was written in parallel and in co-ordination with the writing ECSS-Q-ST-60-03, by the same ECSS Working Group. These two new and complementary standards cover respectively the engineering and the product assurance requirements to be applied when developing ASICs, FPGAs and IP Cores, and these two new standards together supersede ECSS-Q-ST-60-02C.

The DEVICE qualification status is assessed based on the requirements from both ECSS-E-ST-20-40 and ECSS-Q-ST-60-03. In order for a DEVICE to be qualified and accepted according to ECSS standards, the DEVICE development reviews defined in ECSS-E-ST-20-40 have to be declared successful by the customer engineering and PA responsible persons and project management who monitored the DEVICE development.

Scope

This standard defines a comprehensive set of engineering requirements for the successful development of digital, analogue and mixed analogue-digital signal custom designed integrated circuits, such as application specific integrated circuits (ASICs), field programmable gate arrays (FPGAs) and Intellectual Property Cores (IP Cores), from now on referred to with the single and generic term DEVICEs.

Microelectronics systems created by more than one DEVICE die but that are interconnected and packaged together as a single DEVICE are not considered single monolithic DEVICEs. However ECSS-ST-20-40 is to be applied to (a) the development of each individual monolithic die, (b) also for their integration onto a multi-die single DEVICE considering those dice as IP Cores.

This standard may be tailored for the specific characteristic and constraints of a space project in conformance with ECSS-S-ST-00. A pre-tailoring based on the actual DEVICE type and criticality category of the DEVICE is addressed in clause 5.1.2.This standard does not cover requirements for the selection, control, procurement or usage of DEVICEs for space projects nor DEVICE ESCC qualification requirements, as those requirements are covered by ECSS-Q-ST-60C EEE components standard and the ESCC generic specification No. 9000 respectively. Nevertheless, this standard contemplates the possibility for the DEVICE to undergo ESCC qualification after the DEVICE customer acceptance as an ECSS qualified DEVICE, and thus a DEVICE ESCC Detail Specification and DEVICE Radiation Test Plan and Report are optional expected outputs.### Normative references

The following normative documents contain provisions which, through reference in this text, constitute provisions of this ECSS Standard. For dated references, subsequent amendments to, or revisions of any of these publications do not apply. However, parties to agreements based on this ECSS Standard are encouraged to investigate the possibility of applying the most recent editions of the normative documents indicated below. For undated references the latest edition of the publication referred to applies.

|

ECSS-S-ST-00-01

|

ECSS system – Glossary of terms

|

|

ECSS-Q-ST-30

|

Space product assurance – Dependability

|

|

ECSS-Q-ST-40

|

Space product assurance – Safety

|

|

ECSS-Q-ST-60-03

|

Space product assurance – ASIC, FPGA and IP Core product assurance

|

Terms, definitions and abbreviated terms

Terms from other standards

For the purpose of this Standard, the terms and definitions from ECSS-SST0001 apply, in particular the following terms:

- acceptance

- component

- customer

- engineering model

- flight model

- informative

- maintenance

- model

- normative

- performance

- project

- requirement

- risk

- supplier

The old term firmware is defined in ECSS-S-ST-00-01C, and it is not used in the context of ECSS-E-ST-20-40 because with the emergence of new technologies it is now ambiguous and unnecessary. It is important not to confuse terms like FPGA, FPGA programming file or FPGA programming bit stream with firmware.

Terms specific to the present standard

Application Specific Integrated Circuit

full custom or semi custom designed monolithic integrated circuit

ASICs can be digital, analogue or a mixed function.

block diagram

abstract graphical presentation of interconnected named boxes or blocks representing an architectural or functional drawing

Building Block

reusable IC design element that implements a self-standing function or group of functions for which ownership rights exist and that has been developed in the context of a specific IC project or technology, without the intention to be shared with third parties for its reuse in other IC projects

For example, an HDL model such as synthesizable VHDL code, or gate-level netlist, or an analogue function.

cell

specific circuit function including digital or analogue basic blocks

cell library

collection of all mutually compatible cells which conforms to a set of common constraints and standardized interfaces designed and characterized for a specified technology

code

string of words, numbers, letters and symbols that is used to model a DEVICE or its verification and validation environment

For example, Hardware Description Languages like VHDL, Verilog or System-C are used to code DEVICE behavioral or synthesisable models, and code in other languages like C, Python or Tool Command Languages (Tcl) can be used in the DEVICE verification and validation.

data sheet

detailed functional, operational and parametric description of a DEVICE

A data sheet can include, for instance, a block diagram, truth table, pin and signal description, environmental, electrical and performance parameters, tolerances, timing information, and package description.

design for test

technique used to allow a complex integrated circuit to be tested with respect to potential manufacturing faults or to accelerate otherwise too slow validation tests

- 1 For example, any dedicated circuits aimed to provide better observability or commandability of internal nodes of the DEVICE not accessible through primary inputs and outputs.

- 2 Other examples of DFT are test busses, boundary scan as in JTAG, see IEEE 1149.1-2013, built-in self-test, and test modes for functional tests performed at DEVICE Validation, Qualification and Acceptance Phase.

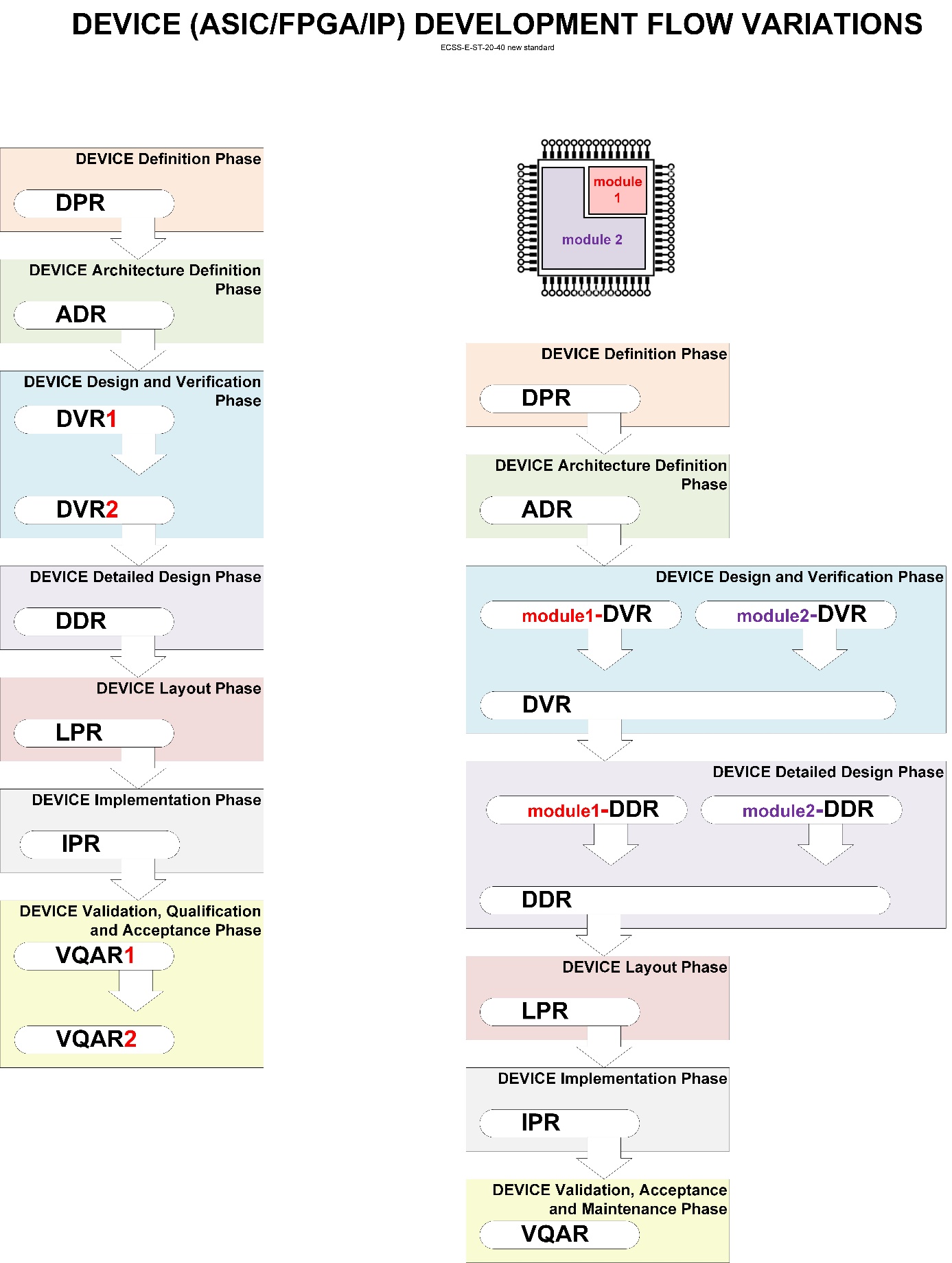

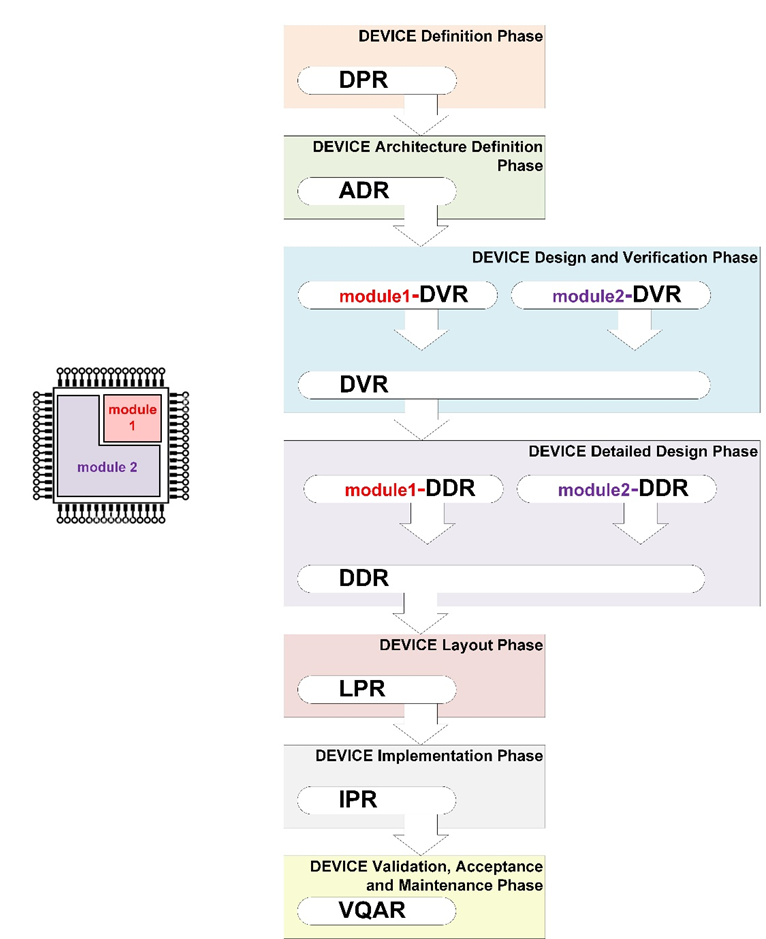

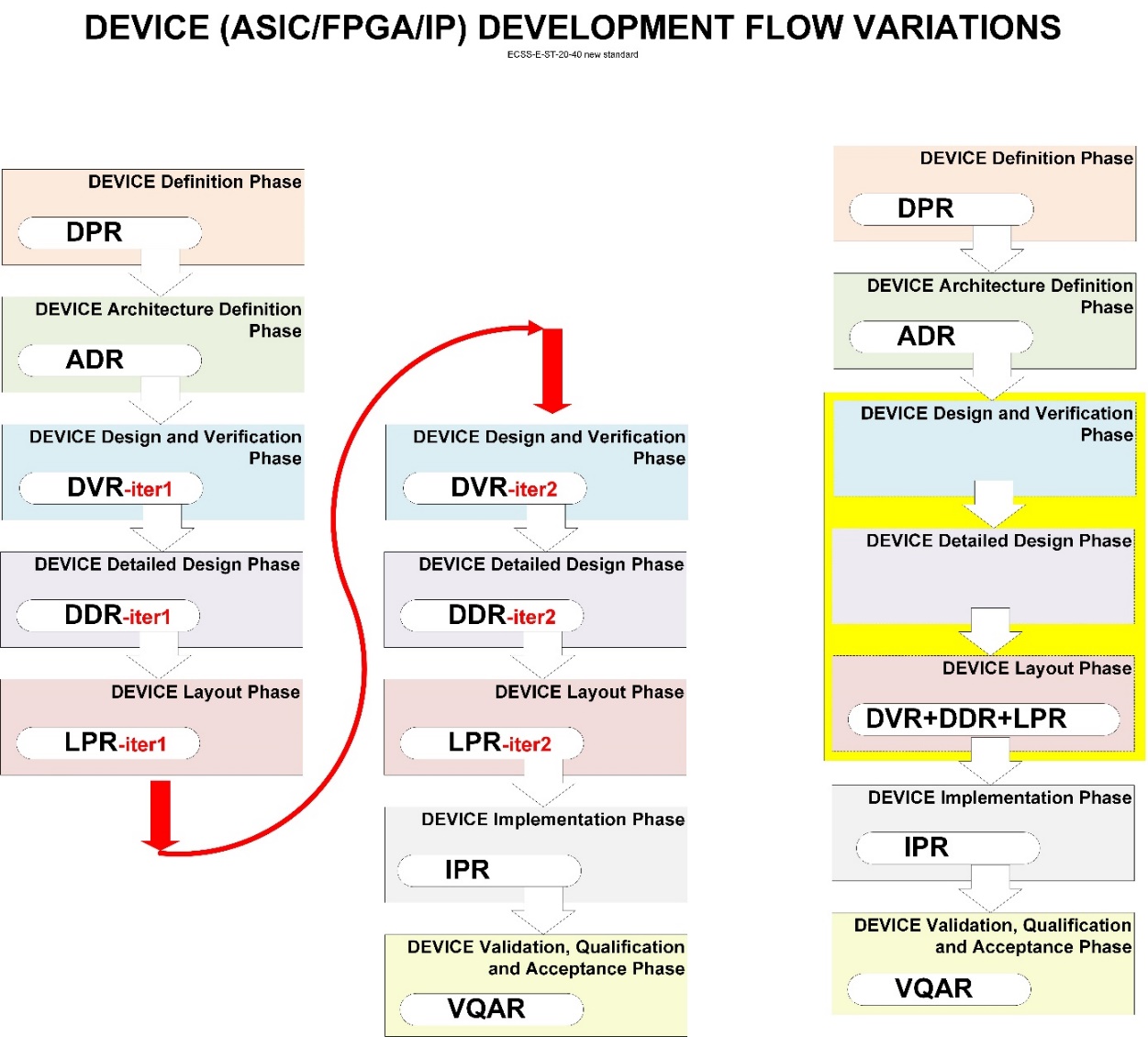

design iteration

design changes that occur in any single phase or between two consecutive phases as defined in the DEVICE Development Plan, before the final DEVICE is released

DEVICE

integrated circuit or an IP Core

-

1 A DEVICE can be a digital, analogue or mixed-signal ASIC, a programmed FPGA, a blank FPGA, a microprocessor, and a model of an IC function that is conceived for reuse as an IP Core.

-

2 A DEVICE can also be a group of dice or chiplets interconnected and integrated inside a single package, such as a system-in-package or a multi-chip-module.

DEVICE Database

set of all digital files that are needed for the development of a DEVICE -

1 Examples of files integrating this database are behavioral and HDL models of the DEVICE, layout description files, models of the DEVICE system environment used to verify by simulation the DEVICE functionality, configuration files and SW programs used for the automation of the verification and validation of the DEVICE, input and output files used and generated by the different CAD tools used, for example files describing the resources, area, timing and power constraints, stimuli and expected output values files, or FPGA bit stream binary files.

-

2 This database of files is incrementally updated throughout the DEVICE development phases, and all necessary elements that enable support, maintenance and a new development of the same or a modified version of the DEVICE can be found in the DEVICE database at the end of the DEVICE Validation, Qualification and Acceptance Phase.

DEVICE development flow

selection and sequence of engineering methods and tools applied during the definition, design, verification, implementation and validation of the DEVICE

DEVICE model

textual or graphical representation of a DEVICE, or a part of it, which defines one or several DEVICE characteristics

-

1 For example, digital or analogue functional behavior, timing performance, power consumption, sizes and interconnections of physical internal structures, input and output external interfaces, environmental effects due to temperature, radiation or aging.

-

2 DEVICE models can be created graphically as graphical design drawings or with textual Hardware Description Languages like VHDL, Verilog, System-C or EDIF.

-

3 DEVICE models can implement several levels of abstraction such as behavioral, Register-Transfer-Level, gate-level netlist or transistor-level, and accuracy such as untimed, loosely timed or approximately timed.

-

4 DEVICE models can be generated manually, assisted by CAD specialized IC design tools or a mix of both.

DEVICE technology

totality of all elements needed for the design, physical implementation and test of either ASIC or FPGA components -

1 For example, design tools and their description, cell libraries, procedures, design rules, manufacturing process, programming tools, test equipment

-

2 Sometimes the terms ASIC technology or FPGA technology are used when referring to the technology of only that type of DEVICE

fault coverage

measure expressed as a percentage of the proportion of actually detectable faults versus all possible faults in a digital circuit, for a given set of test patterns and with respect to a specific fault model

Field Programmable Gate Array

standard semiconductor device that becomes customized when programmed by the user with specific software and hardware tools

FPGA Programming Test

test performed to validate the successful programming of an FPGA

For example, to detect inaccurate programming procedures, incorrect programming files, poor calibration of FPGA programmer, or material defects in the FPGA.

floorplan

abstracted, scaled layout drawing of the die, outlining the form, size and position of the major functional blocks and the pads including power and ground lines, clock distribution and interconnect channels

HDL model

textual description of an integrated circuit based on a hardware description language suitable for the behavioural or structural description and simulation

IP Core

integrated circuit design element that implements a self-standing function or group of functions for which ownership rights exist and is developed for reuse and released with comprehensive verification, validation and documentation

- 1 IP core can be acquired by a customer, for a given price and under an owner-defined license agreement specifying the customer's acquired rights.

- 2 IP core can be supplied as an HDL model, as a synthesizable VHDL code or gate-level netlist, and with the essential complementary documentation that allows the customer to successfully integrate and use it in a system for example User’s Manual and verification files. From this point of view, it can be seen as a semi-finished product.

- 3 IP Cores can be analogue functions provided by DEVICE technology providers as macrocells.

- 4 In contrast with Building Blocks, IP Cores have gone through comprehensive verification, validation and documentation intended for reuse of third parties.

- 5 IP Cores sometimes are referred as hard IPs if they are already placed and routed for one specific IC technology. For example, a macrocell already pre-diffused inside an FPGA or an already layouted function that is included in an ASIC, or a netlist that cannot be modified and is treated as a black-box.

- 6 An IP Core can be composed by combination of different IP Cores.

macrocell

module that contains complex functions in a given technology’s cell library built up out of hard-wired primitive cells

Macrocells can be provided as a library component for ASIC design, for example RAM blocks, or be present inside pre-diffused devices such as DSP blocks or microprocessor cores existing inside FPGAs.

netlist

formatted list of cells, basic circuits, and their interconnections

-

1 The term pre-layout netlist is used for DEVICE netlists that do not contain yet the DEVICE layout information. For example, detailed timing behavior of the cells, timing impact of the interconnections.

-

2 For FPGA, pre-layout netlist means usually the netlist obtained through synthesis tools.

phase

set of interrelated DEVICE development activities -

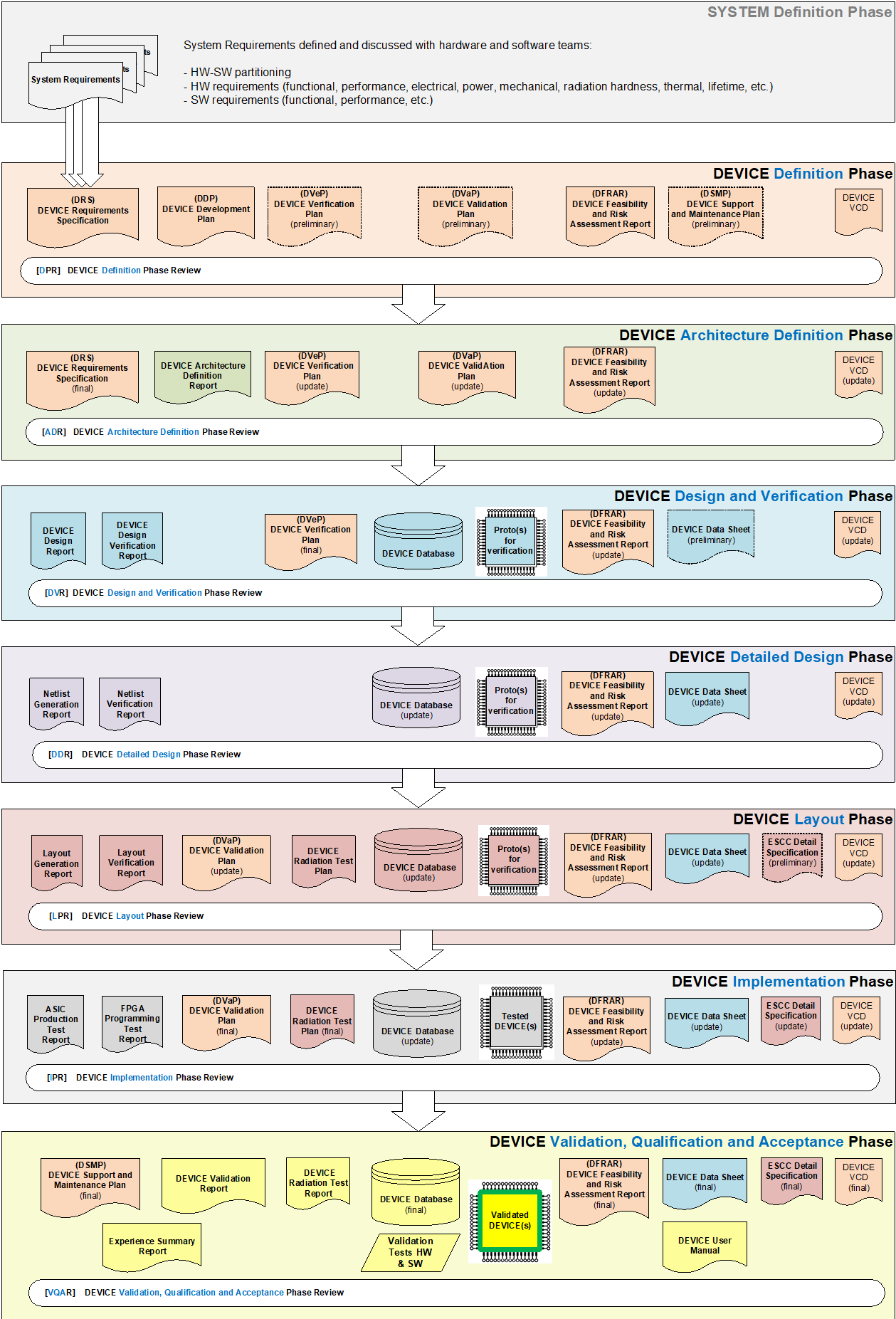

1 A DEVICE generic development flow usually consists of seven phases as depicted in Figure 51. See Annex J for more development flow examples.

-

2 The concept of phase is equivalent to the concept of process defined in ECSS-S-ST-00-01.

processing unit

function which is defined to execute software -

1 The term covers hardware functions such as general purpose processing cores, and more specialized Graphical Processing Unit (GPU), Vision Processing Unit (VPU), Tensor Processing Unit (TPU), Neural Processing Unit (NPU), Physics Processing Unit (PPU), Digital Signal Processor (DSP), or Image Signal Processor (ISP).

-

2 In the context of SW engineering, it also covers software processing units such as interpreters, emulators and virtual machines.

Production Test

test performed on the manufactured DEVICEs to detect functional problems resulting from faults or random material defects during wafer manufacturing, die assembly and packaging -

1 Production Tests are normally performed with test vectors generated by the DEVICE designer and Automatic Test Equipment (ATE) by the DEVICE manufacturer.

-

2 Production Tests include for example stuck-at faults scan tests, timing delay faults, I/O parametric tests for digital ASICs.

-

3 Analogue ASICs Production Tests examples are reference voltage or current tests, AD/DA converters tests or tests to catch manufacturing defects affecting any analogue function.

-

4 Production Tests are not DEVICE Validation tests, which are tests performed on the final DEVICE, ASIC or FPGA, to validate that all requirements in DRS are met. Validation tests are normally performed by the DEVICE development team (the supplier), and not by the DEVICE manufacturer (the foundry), and they include functional, environmental and mechanical tests.

prototype

fabricated ASIC or programmed FPGA used to verify preliminary implementations of the DEVICE against the DEVICE Requirements Specification

redesign

design changes which were not planned in the DEVICE Development Plan and which involve reopening an already closed phase

These design changes can be motivated by unexpected changes in the DRS, wrong interpretation of the DRS or design mistakes.

software

set of instructions and data executed on a processing unit

- 1 A processing unit can be hardware, for example a processor chip, or software, for example a virtual machine or an interpreter.

- 2 Some processing units only require data, for example configuration of state machines or configuration data of a neural network.

- 3 Files using Hardware Description Languages (VHDL, Verilog, System-C) used to model ASICs or bit stream files used to program FPGAs are not software.

stimuli

input data set for simulation or test to show a specific functionality or performance of a DEVICE

synthesis tool

tool that automatically converts a high-level textual representation of an integrated circuit, usually coded in Hardware Description Language at register–transfer-level, into an optimized gate-level netlist representation of the integrated circuit

system requirement

functional, electrical, environmental, mechanical, test or quality requirement of the system wherein the DEVICE is used

Validation

<CONTEXT: ASIC, FPGA, IP Core engineering>

process which demonstrates through the provision of objective evidence that the DEVICE, in its final manufactured (ASIC) or programmed (FPGA) form, is able to perform and behave as expected in the intended system, operational environment and application scenarios

- 1 DEVICE verification is normally performed before DEVICE validation.

- 2 Typical validation methods are hardware tests of the DEVICE integrated in its intended or a representative system, operational environment and application scenarios.

- 3 This term is defined in the present standard with a different meaning than in ECSS-S-ST-00-01. The term with the meaning defined herein is applicable only to the present standard.

Verification

<CONTEXT: ASIC, FPGA, IP Core engineering>

process which demonstrates through the provision of objective evidence that the DEVICE is free of design mistakes and is designed according to its DEVICE Requirements Specification, target technology and manufacturability requirements, as well as any agreed deviations and waivers

- 1 A waiver can arise as an output of the verification process.

- 2 DEVICE verification is normally performed before DEVICE validation

- 3 Verification can be accomplished by one or more of the following methods: analysis (including similarity), simulations of DEVICE models, test of preliminary prototypes, review of design and inspection.

- 4 This term is defined in the present standard with a different meaning than in ECSS-S-ST-00-01. The term with the meaning defined herein is applicable only to the present standard.

Abbreviated terms

For the purpose of this Standard, the abbreviated terms from ECSS-S-ST-00-01 and the following apply:

|

Abbreviation

|

Meaning

|

|

AC

|

alternating current

|

|

ADR

|

DEVICE Architecture Definition Phase Review

|

|

ASIC

|

Application Specific Integrated Circuit

|

|

CAD

|

Computer Aided Design

|

|

DADR

|

DEVICE Architecture Definition Report

|

|

DC

|

direct current

|

|

DDP

|

DEVICE Development Plan

|

|

DDR

|

DEVICE Detailed Design Phase Review

|

|

DDS

|

DEVICE Data Sheet

|

|

DFT

|

design for test

|

|

DPR

|

DEVICE Definition Phase Review

|

|

DRC

|

design rule check

|

|

DRD

|

document requirements definition

|

|

DRS

|

DEVICE Requirements Specification

|

|

DSMP

|

DEVICE Support and Maintenance Plan

|

|

DVaP

|

DEVICE Validation Plan

|

|

DVeP

|

DEVICE Verification Plan

|

|

DVR

|

DEVICE Design and Verification Phase Review

|

|

EDA

|

electronic design automation

|

|

EDIF

|

electronic design interchange format

|

|

EM

|

engineering model

|

|

ERC

|

electrical rule check

|

|

ESCC

|

European Space Components Coordination

|

|

ESD

|

electrostatic discharge

|

|

FM

|

flight model

|

|

FPGA

|

field-programmable gate array

|

|

DFRAR

|

DEVICE Feasibility and Risk Assessment Report

|

|

GDSII

|

graphic design system two (industry standard graphics entry database file format for ASICs)

|

|

HDL

|

hardware description language

|

|

HW

|

hardware

|

|

I/O

|

input-output

|

|

IC

|

integrated circuit

|

|

IEEE

|

Institute of Electrical and Electronics Engineers

|

|

IP

|

intellectual property

|

|

IPR

|

DEVICE Implementation Phase Review

|

|

JTAG

|

joint test action group

|

|

LPR

|

DEVICE Layout Phase Review

|

|

LUT

|

look up table

|

|

MoM

|

minutes of meeting

|

|

P&R

|

place and route

|

|

RTL

|

register-transfer level

|

|

SDF

|

standard delay format

|

|

SEU

|

single event upset

|

|

SPEF

|

standard parasitic exchange format

|

|

SW

|

software

|

|

VQAR

|

DEVICE Validation, Qualification and Acceptance Phase Review

|

|

VCD

|

Verification Control Document

|

|

VHDL

|

Very High Speed Integrated Circuit Hardware Description Language

|

Conventions

Names of DEVICE development phases and reviews

The names of DEVICE development phases and reviews defined in ECSS-E-ST-20-40 do not follow the naming conventions defined in ECSS-M-ST-10 in an effort to use widely established ASIC, FPGA and IP Core engineering terminology which is self-explanatory and commonly used by IC engineers. In order to facilitate collaboration between IC and PA engineers ECSS-E-ST-20-40 provides a comparison between the ECSS-E-ST-20-40 phases and ECSS-M-ST-10 phases and key names in Annex L.

Companies involved in the DEVICE development

In addition to supplier and customer terms used in ECSS standards, the following other terms for other companies that can be part of the DEVICE development are used in ECSS-E-ST-20-40:

FPGA technology provider

ASIC technology provider

ASIC manufacturer

Company developing DEVICE layout

The term technology vendor, even if widely used in the ASIC, FPGA and IP Core community, is avoided in ECSS-E-ST-20-40 in favour of technology provider for the sake of simplicity.

Types of DEVICEs and requirements tailoring tag notation

Find below the basic notation for the different types of DEVICEs in the scope of ECSS-E-ST-20-40 marked in blue color:

|

D-ASIC

|

applicable to fully digital ASICs, or the digital part of mixed-signal ASICs

|

|

A-ASIC

|

applicable to fully analogue ASICs, or the analogue part of mixed-signal ASICs

|

|

FPGA

|

applicable to FPGAs, which can also be mixed-signal DEVICEs

|

|

IP

|

applicable to digital or analogue IP Cores

|

Every requirement in ECSS-E-ST-20-40 contains a “tailoring tag” at the end of the last sentence of the requirement that indicates to which type of DEVICE the requirement is applicable. The tailoring tag can contain one, two or three of the following elements, always in the same order:

[D-ASIC, A-ASIC, FPGA, IP]

If applicable to all four DEVICE types indistinctly, the tag is a simpler

[ALL]

Whenever one of more DEVICEs types shall not be concerned by the requirement, the expression

“-- “

is found in the relevant position. For example

[D-ASIC, A-ASIC, FPGA, --] requirement applicable to all DEVICE types, except for IP Cores.

[--, A-ASIC, --, --] requirement only applicable to analogue ASICs or to the analogue part of mixed-signal ASICs.

[D-ASIC, --, FPGA, IP] requirement applicable to all DEVICE types, except for analogue ASICs.

In the context of ECSS-E-ST-20-40, the development of general purpose complex ICs such as microprocessors, microcontrollers, blank FPGAs or other (re)programmable or extensively configurable DEVICEs commonly known as DSP, GPU, VPU are treated as ASIC developments.

Nomenclature

The following nomenclature applies throughout this document:

The word “shall” is used in this Standard to express requirements. All the requirements are expressed with the word “shall”.

The word “should” is used in this Standard to express recommendations. All the recommendations are expressed with the word “should”.

It is expected that, during tailoring, recommendations in this document are either converted into requirements or tailored out.

The words “may” and “need not” are used in this Standard to express positive and negative permissions, respectively. All the positive permissions are expressed with the word “may”. All the negative permissions are expressed with the words “need not”.

The word “can” is used in this Standard to express capabilities or possibilities, and therefore, if not accompanied by one of the previous words, it implies descriptive text.

In ECSS “may” and “can” have completely different meanings: “may” is normative (permission), and “can” is descriptive.

The present and past tenses are used in this Standard to express statements of fact, and therefore they imply descriptive text.

Principles

DEVICE development

The end-to-end DEVICE development involves several phases. The DEVICE supplier derives from the system requirements WHAT are the functional, performance, environmental and physical requirements that the DEVICE has to meet. The detailed process of HOW the DEVICE will be developed, which includes detailed verification and validation plans, is incrementally defined and implemented by the supplier and reviewed with the customer applying the requirements of ECSS-E-ST-20-40.

The supplier derives requirements and plans of actions for the development of the DEVICE within the boundaries of ECSS-E-ST-20-40. The DEVICE requirements are based on the requirements of the system for which it is intended and take into consideration the operational and environmental requirements of the space project or programme where the DEVICE will be used.

Starting with a global development plan, the verification and validation plans are defined and executed incrementally by the supplier as the DEVICE design progresses through several development phases and until fully verified and validated DEVICEs are accepted by the customer.

Verification methods

Verification methods allow to provide objective evidence that the DEVICE or parts of it are designed according to its requirements specifications and being free of design errors. Such methods can be grouped in five major categories:

ANALYSIS of documents and DEVICE models, often using specialised IC design CAD tools for the analysis of the DEVICE timing, power consumption, resources occupation, parasitic effects, etc.

SIMULATIONS of DEVICE models using IC design CAD tools to perform behavioural and time-accurate simulations of DEVICE internal and output signals obtained when stimuli are applied at DEVICE inputs or internal DEVICE circuit nodes.

TEST of DEVICE hardware prototypes prior to final DEVICE manufacturing or programming.

REVIEW of DEVICE models or circuit schematics performed visually or aided by ad-hoc computer programs. This category includes what is known as review-of-design (ROD) in ECSS-E-ST-10-02.

INSPECTION of the DEVICE hardware. For example, visual inspection of the prototypes used for verification tests in order to check correct mounting on the board or the use of the correct part.

DEVICE engineering

General requirements

Overview

The development of a new DEVICE involves going through a flow of several phases which encompass several engineering steps. It is important to agree with the customer what is the final set of requirements in compliance with ECSS-E-ST-20-40 that are applied and thus define the engineering steps to go through, taking into consideration the type of DEVICE, its criticality category and the specific constraints of the project. In addition, several general requirements apply when defining the DEVICE development flow, when implementing certain recurrent steps in every phase, including the review at the end of each phase which, if successful, implies customer authorisation to start of the next phase.

Tailoring according to DEVICE type and DEVICE criticality

ECSS-E-ST-20-40_1580001Criticality category of the DEVICE under development shall be discussed and agreed with the customer. [ALL]

ECSS-E-ST-20-40_1580002Customer and supplier shall define the final tailoring of the requirements of ECSS-E-ST-20-40 according to the type of DEVICE and according to its criticality category in compliance with clause 6. [ALL]

DEVICE engineering development flow

ECSS-E-ST-20-40_1580003The DEVICE development phases and milestones shall be in conformance with the generic engineering flow presented in Figure 51. [ALL]

- 1 The equivalence of ECSS-M-ST-10 phases and milestone names with respect to ECSS-E-ST-20-40 is presented in Annex L.

- 2 The most complex expected document outputs are defined in DRD annexes, while the content of other expected documents outputs is defined in the main chapters of the standard, and this information is summarized in Table K-2.

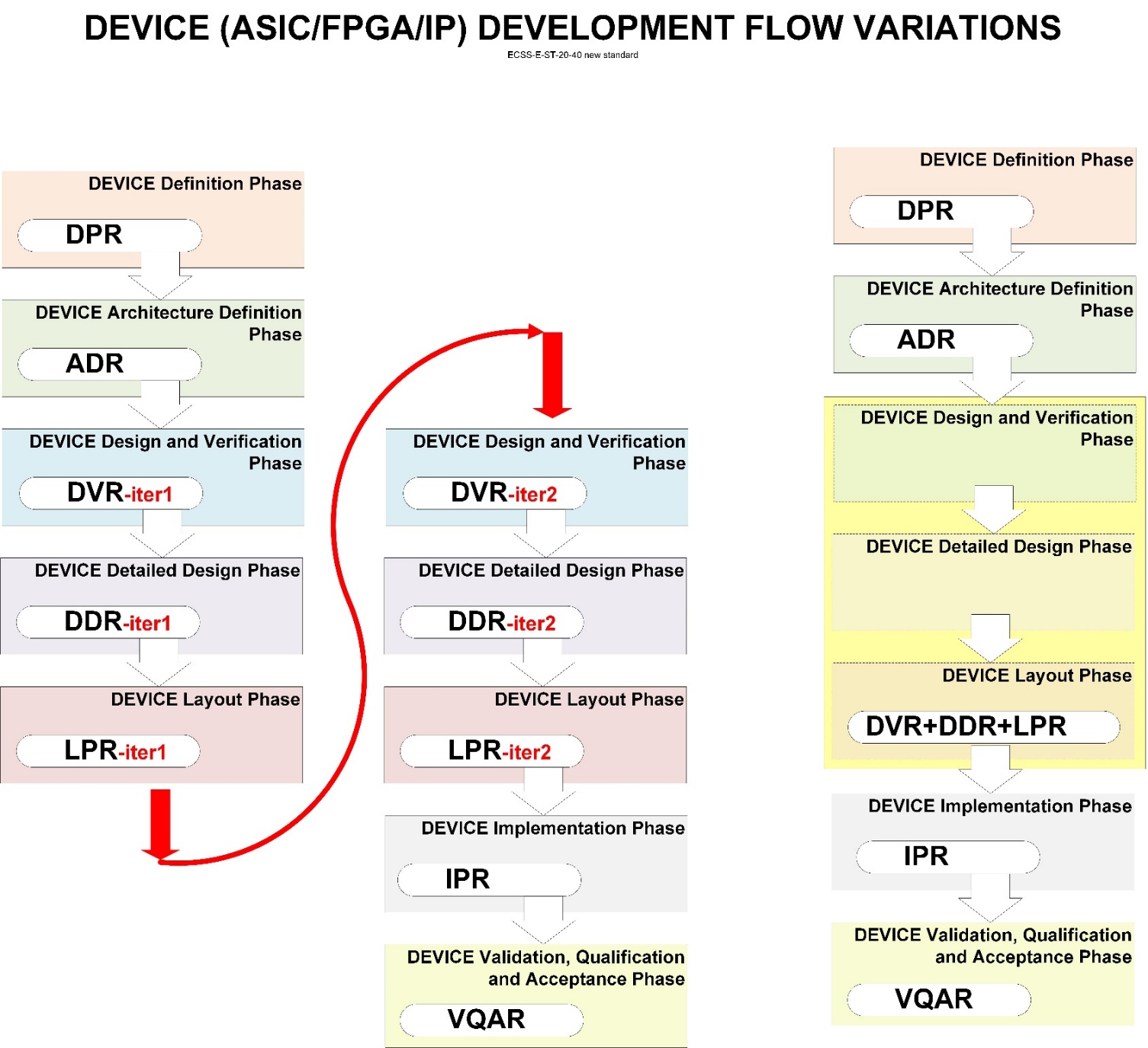

ECSS-E-ST-20-40_1580004If the DEVICE Development Plan includes any variations with respect to the generic flow shown in Figure 51, all the outputs expected at every new phase and associated review shall reflect these changes too. [ALL] - 1 For example, in case of having phase iterations or additional sub-phases and reviews, the Verification and Validation Plans include what requirements are covered in each new phase.

- 2 Annex J describes the main types of DEVICE development flow variations.

ECSS-E-ST-20-40_1580005Each planned additional intermediate step, parallel step or not planned design iteration leading to a new DEVICE database release shall undergo its own dedicated review. [ALL]

ECSS-E-ST-20-40_1580006If the DEVICE development is planned to undergo a first Engineering Model development followed by a Flight Model development, customer and supplier shall agree whether EM and FM are treated as two independent DEVICE developments or as a single DEVICE development where the EM is mainly a prototype verification step for the development of the final FM DEVICE. [ALL] - 1 Treating EM and FM as independent developments can be adequate whenever their respective implementation technologies are significantly different, and therefore the models of EM and FM DEVICEs are significantly different too.

- 2 Treating EM and FM as independent developments can also be adequate if EM DEVICE is planned to be used as a stand-alone product and not just as an intermediate verification step for the FM DEVICE.

ECSS-E-ST-20-40_1580007All inputs and tools used to reproduce DEVICE development steps in every phase shall follow the documentation and configuration management requirements in compliance with clause 8 of ECSS-Q-ST-60-03. [ALL] - 1 Examples of such inputs are simulation test patterns, schematics, VHDL source codes and synthesis scripts.

- 2 Examples of DEVICE development steps are netlist generation and netlist verification.

- 3 Tools are any design, verification and validation software and hardware tools used during the DEVICE development.

ECSS-E-ST-20-40_1580008The supplier shall ensure automatic repeatability of all development steps that make use of CAD tools that support automation in order to facilitate iterations in the flow. [ALL]

Examples of planned iterations include repetitions of self-checking simulations as the design is maturing. But iterations in the development flow can also be needed due to unexpected changes to the requirements, the technology or any unforeseen modifications to the design

ECSS-E-ST-20-40_1580009In order to reopen a phase that was successfully closed already, supplier and customer shall discuss and reach an agreement on it. [ALL]

ECSS-E-ST-20-40_1580010Every output shall be updated at the end of every phase with any relevant new information gathered during the phase. [ALL]

Phase Reviews

ECSS-E-ST-20-40_1580011The outputs generated within each phase shall be reviewed by the customer with the support of the supplier. [ALL]

ECSS-E-ST-20-40_1580012The reviewers shall analyse the preventive measures and contingency plans for all identified open issues and risk items identified in the DEVICE Feasibility and Risk Assessment to define and agree with the customer the risks that are taken for starting the next phase. [ALL]

ECSS-E-ST-20-40_1580013The reviewers shall check that all expected outputs contain all the relevant information and with a level of detail that avoids ambiguity. [ALL]

ECSS-E-ST-20-40_1580014Any missing information and open points and their impact on following phases shall be assessed, registered and agreed with the customer in the MoM of the phase review with an indication of the expected time of completion of the open points. [ALL]

ECSS-E-ST-20-40_1580015The criteria for a successful phase review shall be defined in advance. [ALL]

ECSS-E-ST-20-40_1580016Phase reviews shall be conducted in accordance with ECSS-M-ST-10 and ECSS-M-ST-10-01. [ALL]

DEVICE Verification Control Document

ECSS-E-ST-20-40_1580017At DEVICE Definition Phase review the supplier shall provide for customer approval an initial DEVICE VCD, in compliance with ECSS-E-ST-10-02 Annex B VDC DRD, including [ALL]

the DEVICE requirements with the combination of the selected verification and validation methods for the different verification and validation levels at the applicable development phases and the applicable verification stages.

The traceability between DEVICE requirements and System requirements in compliance with ECSS-E-ST-10-06 clause 8.2.3.

- 1 Verification stages can be qualification, acceptance, prelaunch, in-orbit (including commissioning) and postlanding, as defined in ECSS-E-ST-10-02 clause 4.2.4.

- 2 Verification methods are defined in ECSS-E-ST-20-40 clause 4.2.

- 3 Some verification and validation information can be found in ECSS-E-ST-20-40 reports and used to populate parts of the VCD. These reports are Design Verification Report, Netlist Verification Report, Layout Verification Report, ASIC Production Test Report, FPGA Programming Test Report, DEVICE Validation Report and Radiation Test Report.

- 4 References to relevant sections of the DVerP, DValP, or reports, waivers, RFD, NCR, NRB or customer closeout reports can be added to VCD to demonstrate compliance with the requirements.

- 5 The DEVICE VCD can be included in the upper level VCD, for example, equipment or unit VCD.

ECSS-E-ST-20-40_1580018The supplier shall provide for customer approval an updated DEVICE VCD with the verification and validation close out status for the DEVICE at each phase review in compliance with ECSS-E-ST-10-02 Annex B VCD DRD. [ALL]

Figure 51: DEVICE development flow (generic case)

Figure 51: DEVICE development flow (generic case)

DEVICE Definition Phase

Overview

The aim of this initial DEVICE Definition Phase is to establish a DEVICE Development Plan that defines the development flow, indicating the resources and schedules, a DEVICE Requirements Specification that results from carefully flowing down the requirements of the system(s) where the DEVICE is used and ensuring good traceability between the DEVICE requirements and the System Requirements. In addition, a Feasibility and Risk Assessment of the DEVICE development is an important part of this initial DEVICE Definition Phase and is revised in the following phases in order to minimise risks.

DEVICE Requirements Specification

ECSS-E-ST-20-40_1580019The supplier shall specify the complete set of DEVICE requirements in the DEVICE Requirements Specification in compliance with DRD from Annex A. [ALL]

ECSS-E-ST-20-40_1580020The supplier shall ensure that all System Requirements that are relevant to the DEVICE are flowed down to the DRS allowing back traceability. [ALL]

ECSS-E-ST-20-40_1580021If the DEVICE contains one or more processing unit, the supplier shall flow the HW-SW partitioning requirements in the System Requirements down into the DEVICE Requirements Specification. [D-ASIC, --, FPGA, IP]

HW-SW partitioning is usually done by the System team, often the customer, in collaboration with HW and SW development teams (see requirement 5.2.2.4.a of ECSS-E-ST-40).

DEVICE Development Plan

ECSS-E-ST-20-40_1580022The supplier shall provide the customer with a complete description of the DEVICE development global strategy in the DEVICE Development Plan which in compliance with DRD from Annex B. [ALL]

ECSS-E-ST-20-40_1580023The development methodology of any subcontractors in charge of developing any of the Building Blocks for the DEVICE shall be ascertained by the supplier and agreed with the customer. [ALL]

For example, whether deviations or tailoring to ECSS-E-ST-20-40 are applied.

ECSS-E-ST-20-40_1580024Design and verification responsibilities shall be assigned to different people in order to guarantee independent verification. [ALL]

For example, the FPGA Responsible Engineer can take over the role of the FPGA Designer or of the FPGA Verification Engineer, but not both.

ECSS-E-ST-20-40_1580025If the DEVICE contains one or more processing units, the supplier shall plan and document how to synchronise the DEVICE development flow key milestones with the System and SW development flows key milestones in order to manage dependencies between DEVICE, SW and System developments. [D-ASIC, --, FPGA, IP]

ECSS-E-ST-20-40_1580026If the DEVICE contains both analogue and digital blocks, the supplier shall plan and document how to synchronise the DEVICE development flow key milestones with the analogue and digital development flows key milestones in order to manage dependencies. [ALL]

ECSS-E-ST-20-40_1580027Modifications to IP Cores shall be justified and agreed between supplier and customer, documented in the DDP, DVeP and DVaP, specified in DRDs of Annex B, Annex C, and Annex D, and updated accordingly whenever these modifications are agreed. [ALL]

Preliminary Verification and Validation Plans

ECSS-E-ST-20-40_1580028The supplier shall define the general approach to verifying and validating the DEVICE in preliminary Verification and Validation Plans in compliance with DRDs from Annex C and Annex D. [ALL]

ECSS-E-ST-20-40_1580029The supplier shall include the different types of verification and validation methods and test procedures, and a preliminary matrix for the traceability. [ALL]

For example, which parts of the DEVICE are verified and validated separately, whether or not preliminary HW prototypes are used for DEVICE verification, specific Design-for-Test and test modes needed to accelerate otherwise too lengthy verification or validation steps, verification and validation approach when processing units are part of the DEVICE.

ECSS-E-ST-20-40_1580030Modified IP Cores shall be treated as Building Blocks that undergo full verification and validation. [ALL]

Preliminary DEVICE Support and Maintenance Plan

ECSS-E-ST-20-40_1580031If agreed between supplier and customer a preliminary DEVICE Support and Maintenance Plan shall be produced by the supplier in compliance with DRD from Annex E. [ALL]

Feasibility and Risk Assessment

ECSS-E-ST-20-40_1580032The supplier shall perform a feasibility and risk assessment of the development of the DEVICE and document it in the DEVICE Feasibility and Risk Assessment Report in compliance with DRD in Annex F. [ALL]

DEVICE Definition Phase Review

ECSS-E-ST-20-40_1580033The DEVICE Definition Phase shall be concluded by a DEVICE Definition Phase Review in compliance with requirements from clause 5.1.4. [ALL]

ECSS-E-ST-20-40_1580034The reviewers shall check that the DEVICE development activity as defined in the DDP as in DRD in Annex B is feasible within the limits imposed by the project requirements, resources, schedule and budgetary constraints. [ALL]

ECSS-E-ST-20-40_1580035The following expected outputs shall be reviewed during DEVICE Definition Phase Review: [ALL]

- DEVICE Requirements Specification (DRS) as in DRD in Annex A

- DEVICE Development Plan (DDP) as in DRD in Annex B

- DEVICE Verification Plan (preliminary) as in DRD in Annex C

- DEVICE Validation Plan (preliminary) as in DRD in Annex D

- DEVICE Support and Maintenance Plan (preliminary) as in DRD in Annex E

- DEVICE Feasibility and Risk Assessment Report (DFRAR) as in DRD in Annex F

- DEVICE VCD (preliminary)

DEVICE Architecture Definition Phase

Overview

The aim of this development phase is to define the architecture of the DEVICE design in terms of its main functional blocks, hierarchies and dependencies of these blocks, their interfaces and how they interconnect. The objective is to facilitate the modular and detailed design of all the blocks and their integration in the following phases.

Architecture Definition

ECSS-E-ST-20-40_1580036The supplier shall define the DEVICE architecture and document it in the DEVICE Architecture Definition Report in compliance with DRD in Annex G. [ALL]

ECSS-E-ST-20-40_1580037Any pertinent additions and modifications to the DRS of DRD in Annex A due to the DEVICE architecture definitions shall be included in a final DRS. [ALL]

This is done in order to guide the DEVICE designers’ work in the lower-level DEVICE Design and Verification Phase and later in the DEVICE Detailed Design Phase.

Updated DEVICE Verification and Validation Plans

ECSS-E-ST-20-40_1580038The supplier shall update and maintain the preliminary DEVICE Verification and Validation Plans in accordance with Annex C and Annex D, defining verification methods and validation test procedures for requirements impacting the DEVICE architecture definition. [ALL]

For example, test procedures to validate radiation effects mitigation techniques introduced at DEVICE architectural level or HW-SW interfaces and functional dependencies.

DEVICE Architecture Definition Phase Review

ECSS-E-ST-20-40_1580039The DEVICE Architecture Definition Phase shall be concluded by a DEVICE Architecture Definition Phase Review in compliance with requirements from clause 5.1.4. [ALL]

ECSS-E-ST-20-40_1580040The reviewers shall check that the selected architectural trade-offs meet the requirements fixed during the DEVICE Definition Phase. [ALL]

ECSS-E-ST-20-40_1580041The following expected outputs shall be reviewed during DEVICE Architecture Definition Phase Review: [ALL]

- DEVICE Architecture Definition Report as in DRD in Annex G

- DEVICE Requirements Specification (final) as in DRD in Annex A.

- DEVICE Verification plan (update) (DVeP) as in DRD in Annex C

- DEVICE Validation Plan (update) (DVaP) as in DRD in Annex D

- DEVICE Feasibility and Risk Assessment Report (update) (DFRAR) as in DRD in Annex F

- DEVICE VCD (update)

DEVICE Design and Verification Phase

Overview

The aim of the DEVICE Design and Verification Phase is to further develop the DEVICE creating the first DEVICE models and their verification environment. These models are part of the DEVICE Database. The DEVICE model creation and its verification is documented in the DEVICE Design Report and the DEVICE Design Verification Report respectively, a preliminary DEVICE Data Sheet is prepared, and the phase concludes with the DEVICE Design and Verification Phase Review securing that everything is ready for the DEVICE Detailed Design Phase.

DEVICE Verification Plan

ECSS-E-ST-20-40_1580042A DEVICE Verification Plan in compliance with DRD in Annex C shall be completed and ready at DEVICE Design and Verification Phase Review. [ALL]

DEVICE Design and Verification

ECSS-E-ST-20-40_1580043Tasks specified in requirements 5.4.3b to 5.4.3j shall be performed and documented by the supplier in a DEVICE Design Report. [ALL]

ECSS-E-ST-20-40_1580044The supplier shall generate the DEVICE models needed as input to the subsequent DEVICE Detailed Design Phase. [ALL]

- 1 For example, synthesizable RTL models for digital circuits, or behavioral models for analogue circuits.

- 2 Simulations of DEVICE behavioral models of critical functions and algorithms can be very useful during the DEVICE Architecture Definition Phase and Feasibility and Risk Assessment, as they can be valuable tools for further verification tasks.

ECSS-E-ST-20-40_1580045The supplier shall model analogue block interfaces, drivers and loads including their estimated parasitics. [--, A-ASIC, --, --]

For example, parasitics introduced by the package, bonding or wiring tracks.

ECSS-E-ST-20-40_1580046The supplier shall perform an analysis of key analogue parameters and their sensitivity to manufacturing and environmental variations in order to consequently protect the DEVICE analogue blocks against those variations. [--, A-ASIC, --, --]

For example, parameters such as circuit dimensions or electrical parameters which can be affected by process manufacturing and external T, V or I variations.

ECSS-E-ST-20-40_1580047The supplier shall define and document the global approach to integration of new and existing Building Blocks and IP Cores up until the entire DEVICE is integrated at top level. [ALL]

ECSS-E-ST-20-40_1580048The supplier shall generate the necessary DEVICE verification files, verify the DEVICE models following the DEVICE Verification Plan of DRD in Annex C and document results in the first iteration of the DEVICE Design Verification Report. [ALL]

Verification files examples are HDL simulation testbenches, external components models, and data files defining stimuli and expected outputs.

ECSS-E-ST-20-40_1580049The supplier shall perform a preliminary floorplan and a preliminary technology mapping to ensure a successful place-and-route and timing closure in cases where this early assessment can be of added value. [D-ASIC, A-ASIC, FPGA,--]

Technology mapping for digital circuits can be achieved for example by synthesis tools that transform RTL models into gate-level netlists.

ECSS-E-ST-20-40_1580050The supplier shall re-assess the feasibility and risks, including trade-offs for any conflicting requirements, update the DFRAR and implement the best design choices accordingly. [ALL]

For example, power consumption versus speed and performance, pin count versus package size and complexity versus die area, update the DFRAR and implement the best design choices accordingly.

ECSS-E-ST-20-40_1580051The supplier shall specify the configuration applied to IP Cores used in the DEVICE. [ALL]

ECSS-E-ST-20-40_1580052The supplier shall specify any modifications done to IP Cores as justified in the DFRAR and agreed between supplier and customer. [ALL]

ECSS-E-ST-20-40_1580053The radiation hardening approach shall be implemented and verified at this development level. [ALL]

For example, TMR, safe state machines or error detection and correction at RTL HDL level.

DEVICE Database

ECSS-E-ST-20-40_1580054The supplier shall create and maintain a DEVICE Database with all the files needed as inputs for the DEVICE Detailed Design Phase and phase reiterations, including items specified in 5.4.4b to 5.4.4d. [ALL]

ECSS-E-ST-20-40_1580055The DEVICE Database shall include the DEVICE models and other electronic files needed for the complete DEVICE netlist generation. [ALL]

For example, high-level simulation, behavioral and RTL models and analogue design models.

ECSS-E-ST-20-40_1580056The DEVICE Database shall include the executable and script files used for verification of the DEVICE models. [ALL]

For example, testbenches, simulation control or constraint files, external component models, stimuli input files and expected output files, ad-hoc executable files to process verification results and results log files.

ECSS-E-ST-20-40_1580057The DEVICE Database shall include the description of what the DEVICE Database contains, including the files’ structure, naming conventions and version control labels. [ALL]

Preliminary DEVICE Data Sheet

ECSS-E-ST-20-40_1580058If agreed with the customer, the supplier shall generate a preliminary DEVICE Data Sheet in compliance with DRD from Annex H. [ALL]

- 1 Data Sheets are in general intended for users of the DEVICE who do not have access to the DEVICE development documents such as the DEVICE Requirements Specification.

- 2 For example, if the DEVICE is marketed as an off-the-shelf product.

- 3 Some of the DEVICE technical parameters are inherent to the technology used to implement the DEVICE and therefore can be provided by the technology provider for example in the form of blank FPGA Data Sheets or ASIC manufacturer and standard cell library documents.

ECSS-E-ST-20-40_1580059The preliminary DEVICE Data Sheet shall contain all parts of the final DEVICE Data Sheet, with the same level of detail, using clearly identified estimated values for those parameter values that are not yet confirmed. [ALL]

For example, preliminary values can be obtained by simulation or measurements on a prototype, while final parameter values are confirmed with the validated DEVICE.

ECSS-E-ST-20-40_1580060The preliminary DEVICE Data Sheet shall contain at least the main functionalities and interfaces of the DEVICE. [ALL]

This information can be provided in the form of Interface Control Document (ICD) as defined in ECSS-E-ST-40 Annex E.

DEVICE Design and Verification Phase Review

ECSS-E-ST-20-40_1580061The DEVICE Design and Verification Phase shall be concluded by the DEVICE Design and Verification Phase Review in compliance with requirements from clause 5.1.4. [ALL]

ECSS-E-ST-20-40_1580062The following expected outputs shall be reviewed during DEVICE Design and Verification Phase Review: [ALL]

- DEVICE Verification Plan (final) (DVeP) as in DRD in Annex C

- DEVICE Design Report

- DEVICE Design Verification Report

- DEVICE Data Sheet (preliminary) as in DRD in Annex H

- DEVICE database

- DEVICE Feasibility and Risk Assessment Report (update) (DFRAR) as in DRD in Annex F

- DEVICE VCD (update)

DEVICE Detailed Design Phase

Overview

During the DEVICE Detailed Design Phase, the DEVICE design is translated into a structural description at the level of elementary cells of the selected technology and cell library: the pre-layout netlist.

Additional information is generated for the subsequent development phases, such as layout constraints, floorplanning, Production Tests programs and a detailed pin description.

For digital designs, the above-mentioned design description is the technology specific gate-level pre-layout netlist normally obtained by synthesis tools.

For analogue designs, it is a verified sized transistor-level netlist. However, in many analogue designs, there is no separation between circuit netlist design and layout.

Meeting DEVICE timing, occupancy and power targets sometimes can need performing iterations between netlist generation and layout generation.

Netlist Generation

ECSS-E-ST-20-40_1580063Tasks specified in requirements 5.5.2b to 5.5.2u shall be performed and documented by the supplier in a Netlist Generation Report. [ALL]

ECSS-E-ST-20-40_1580064The supplier shall confirm use of design tools version as specified in the DEVICE Development Plan of DRD in Annex B, including the tools maintenance status, known bugs and existing patches. [ALL]

ECSS-E-ST-20-40_1580065The supplier shall choose and implement the pre-layout netlist generation with the selected tool options and constraints. [ALL]

For example, script variables and commands to control the timing, area, power, types of library cells used or different synthesis modes for complex DEVICEs.

ECSS-E-ST-20-40_1580066Clock, reset or other signals needing specific generation, buffering and delay-controlled distribution with high fan-out shall be implemented using available netlist generation resources. [D-ASIC, A-ASIC, FPGA, --]

These buffers and signal distribution trees can be implemented during the Layout Phase also, depending on what is the target implementation technology.

ECSS-E-ST-20-40_1580067DFT and Production Tests requirements shall be implemented. [ALL]

ECSS-E-ST-20-40_1580068The radiation hardening approach shall be implemented and verified at netlist level. [ALL]

For example, TMR, safe state machines or error detection and correction generated by netlist synthesis tools.

ECSS-E-ST-20-40_1580069A floorplan shall be defined or refined if already existing. [ALL]

ECSS-E-ST-20-40_1580070I/O buffers and interfaces shall be confirmed and implemented. [ALL]

For example, HSSL, LVDS, tri-state buffers, etc.

ECSS-E-ST-20-40_1580071The supplier shall implement design parameter centring based on simulations, allowing margins that account for final layout and process variations, in order to maximise yield. [--, A-ASIC, --, IP]

ECSS-E-ST-20-40_1580072The supplier shall justify and document any library cells selections. [D-ASIC, A-ASIC, --, IP]

For example, some cells can be excluded from being used due to their weaker radiation performance, or some specific cells get higher priority in being used due to their more favorable timing characteristics.

ECSS-E-ST-20-40_1580073The supplier shall describe any logic cells that were specially developed for the DEVICE. [D-ASIC, A-ASIC, --, IP]

For example, to achieve higher radiation tolerance, to meet testability, manufacturability or power consumption DRS requirements, or to meet technology provider constraints.

ECSS-E-ST-20-40_1580074The supplier shall describe any Design-For-Manufacturability strategies applied during netlist generation. [D-ASIC, A-ASIC, --, --]

ECSS-E-ST-20-40_1580075The supplier shall specify and justify the use of any black-boxes in the netlist. [ALL]

For example, elements of the netlist that cannot be modified by using specific synthesis tool attributes or that cannot be interpreted by synthesis tool, or netlist blocks which are added at a later stage.

ECSS-E-ST-20-40_1580076The supplier shall document all settings applied during netlist generation, including those related to technology supplier or manufacturer-specific design rules. [ALL]

For example, timing, area or power constraints, process variations, temperature and voltage operating conditions, radiation environment constraints and IP Core synthesis constraints provided by the IP provider.

ECSS-E-ST-20-40_1580077Level of utilization of available resources shall be determined and documented. [ALL]

For example, the number of logic and memory cells used, and number of clock and reset dedicated buffers.

ECSS-E-ST-20-40_1580078The supplier shall specify the configuration and netlist generation constraints applied to IP Cores used in the DEVICE netlist. [ALL]

ECSS-E-ST-20-40_1580079Any deviations from IP Core provider recommendations for the netlist generation of the IP Core shall be documented and justified. [ALL]

ECSS-E-ST-20-40_1580080The supplier shall document any applied derating factors. [ALL]

For example, derating factors for timing, current density or power.

ECSS-E-ST-20-40_1580081The supplier shall document any applied margins. [ALL]

For example, margins for timing, area, number of I/Os, LUT or memory blocks.

ECSS-E-ST-20-40_1580082Influences from layout such as cross talk and matching shall be accounted for during the detail design work. [D-ASIC, A-ASIC, --, IP]

ECSS-E-ST-20-40_1580083The supplier shall document how parasitic effects are dealt with. [D-ASIC, A-ASIC, --, IP]

Netlist verification

ECSS-E-ST-20-40_1580084Tasks specified in requirements 5.5.3b to 5.5.3c shall be performed and documented by the supplier in a Netlist Verification Report. [ALL]

ECSS-E-ST-20-40_1580085Verification of the netlist shall be performed in compliance to the DEVICE Verification Plan of DRD in Annex C. [ALL]

ECSS-E-ST-20-40_1580086If Production Tests and functional test modes are planned, the supplier shall generate preliminary test vectors and verify the related DEVICE requirements. [ALL]

DEVICE Data Sheet update

ECSS-E-ST-20-40_1580087The supplier shall update the preliminary DEVICE Data Sheet of DRD in Annex H according to the results obtained during the DEVICE Detailed Design Phase. [ALL]

For example, new information about timing, power consumption, pin-out and resources occupation parameters.

DEVICE Database update

ECSS-E-ST-20-40_1580088The supplier shall update the DEVICE Database with the input files needed for the following DEVICE Layout and Implementation phases, including items specified in 5.5.5b to 5.5.5f. [ALL]

ECSS-E-ST-20-40_1580089The DEVICE Database shall include the pre-layout netlist. [ALL]

ECSS-E-ST-20-40_1580090The DEVICE Database shall include the preliminary set of constraints for layout. [ALL]

For example, a DEVICE floorplan, or timing, power and area constraints. [ALL]

ECSS-E-ST-20-40_1580091The DEVICE Database shall include the preliminary test vectors for Production Tests. [D-ASIC, A-ASIC, --, --]

ECSS-E-ST-20-40_1580092The DEVICE Database shall include the scripts used for an automatic and repeatable generation of the netlist and its verification, and the corresponding result log files. [D-ASIC, A-ASIC, FPGA, --]

ECSS-E-ST-20-40_1580093DEVICE Database description of files structure, naming conventions, and version control labels shall be updated to reflect all the changes. [ALL]

DEVICE Detailed Design Phase Review

ECSS-E-ST-20-40_1580094The DEVICE Detailed Design Phase shall be concluded by the DEVICE Detailed Design Phase Review in compliance with requirements from clause 5.1.4. [ALL]

ECSS-E-ST-20-40_1580095The reviewers shall confirm the complete list of items with name and format to be provided to the company developing the DEVICE layout and manufacturing. [D-ASIC, A-ASIC, --, -- ]

For example, pre-layout netlist files, stimuli files for Production Tests and constraints files.

ECSS-E-ST-20-40_1580096The following expected outputs shall be reviewed during DEVICE Detailed Design Phase Review: [ALL]

- Netlist Generation Report

- Netlist Verification Report

- DEVICE Data Sheet (update) as in DRD in Annex H

- DEVICE Database (update)

- DEVICE VCD (update)

- DEVICE Feasibility and Risk Assessment Report (update) (DFRAR) as in DRD in Annex F

DEVICE Layout Phase

Overview

The aim of the DEVICE Layout Phase is to generate a structural description of the DEVICE at the level of elementary cells of the selected technology and libraries creating a placed and routed model of the netlist and all the complementary files that are needed to manufacture or program the DEVICE.

Layout generation

ECSS-E-ST-20-40_1580097Tasks specified in requirements 5.6.2b to 5.6.2p shall be performed and documented by the supplier in a Layout Generation Report. [ALL]

ECSS-E-ST-20-40_1580098Floorplan of the DEVICE shall be finalised. [D-ASIC, A-ASIC, FPGA, --]

ECSS-E-ST-20-40_1580099The core and I/O-pad power distribution shall be generated. [D-ASIC, A-ASIC, --, --]

ECSS-E-ST-20-40_1580100Test pads, if needed, shall be generated. [D-ASIC, A-ASIC, --, --]

ECSS-E-ST-20-40_1580101The bonding diagram respecting bonding and package constraints shall be generated. [D-ASIC, A-ASIC, --, --]

ECSS-E-ST-20-40_1580102ESD protection circuits shall be generated. [D-ASIC, A-ASIC, --, --]

ECSS-E-ST-20-40_1580103The clock distribution, including clock tree and buffers shall be generated. [D-ASIC, --, --, --]

ECSS-E-ST-20-40_1580104Any other global networks that need place and route decisions shall be generated. [D-ASIC, --, --, --]

For example, reset networks.

ECSS-E-ST-20-40_1580105Final set of constraints and options for the layout generation shall be selected. [D-ASIC, --, FPGA, --]

For example, timing and physical resources.

ECSS-E-ST-20-40_1580106Place and route shall be performed applying all layout constraints. [D-ASIC, --, FPGA, --]

For example, timing and physical resources constraints.

ECSS-E-ST-20-40_1580107Final resources utilization shall be determined. [ALL]

For example, die size, number of logic elements, pre-diffused signal and power networks, in case of FPGAs, and number of I/Os.

ECSS-E-ST-20-40_1580108The supplier shall describe any Design-For-Manufacturability strategies applied during layout generation. [D-ASIC, A-ASIC, --, --]

ECSS-E-ST-20-40_1580109The radiation hardening approach shall be implemented and verified at layout level. [ALL]

For example, laying out asynchronous signal paths with filtering buffers or shaping the topology, widths and lengths of active areas of critical cells and the distances between them.

ECSS-E-ST-20-40_1580110The final ASIC post-layout netlist shall be generated applying manufacturer constraints and design rules and the new timing data extracted from the layout. [D-ASIC, --, --, --]

For example, the pre-layout netlist can be optimized by local re-synthesis or physical or topography synthesis in order to obtain the final post-layout netlist.

ECSS-E-ST-20-40_1580111The final FPGA place and route database files needed for the verification of the FPGA layout shall be generated. [--, --, FPGA, --]

For example, timing files such as SDF used for netlist timing simulation or static timing analysis, pin out assignment reports or power consumption reports.

ECSS-E-ST-20-40_1580112Input files needed for the generation of the ASIC masks or for the FPGA programming shall be generated. [D-ASIC, A-ASIC, FPGA, --]

For example, GDSII files for ASICs or programming bit stream files for FPGAs.

Layout verification

ECSS-E-ST-20-40_1580113The supplier shall perform comprehensive layout and post-layout or post-place-and-route netlist verification according to the DEVICE Verification Plan specified in DRD in Annex C and document the results in the Layout Verification Report. [D-ASIC, A-ASIC, FPGA, --]

ECSS-E-ST-20-40_1580114Major warnings and deviations from technology provider rules found during verification shall be analysed and reported in the Layout Verification Report. [D-ASIC, A-ASIC, FPGA, --]

DEVICE Validation Plan

ECSS-E-ST-20-40_1580115The supplier shall complete and consolidate the final DEVICE Validation Plan detailing all the validation test procedures to be carried out and in compliance with DRD in Annex D. [ALL]

ECSS-E-ST-20-40_1580116If agreed with the customer, radiation test procedures shall be defined and documented in a dedicated DEVICE Radiation Test Plan. [ALL]

DEVICE Database update

ECSS-E-ST-20-40_1580117Files generated during DEVICE Detailed Design Phase shall be added to the DEVICE Database. [D-ASIC, A-ASIC, FPGA, --]

For example, post-layout netlist, SDF files, FPGA bit stream files and ASIC GDSII files.

ECSS-E-ST-20-40_1580118The DEVICE Database shall include the scripts used for an automatic and repeatable generation of the layout files and their verification, and the corresponding result log files. [D-ASIC, A-ASIC, FPGA, --]

ECSS-E-ST-20-40_1580119The DEVICE Database description of files structure, naming conventions, version control labels shall be updated to reflect all the changes. [D-ASIC, A-ASIC, FPGA, --]

DEVICE Data Sheet update

ECSS-E-ST-20-40_1580120The supplier shall update the parameters in the DEVICE Data Sheet of DRD in Annex H according to the results obtained during the layout verification. [ALL]

For further details see Annex H.

Preliminary ESCC Detail Specification

ECSS-E-ST-20-40_1580121If agreed between supplier and customer, a preliminary ESCC Detail Specification shall be established in conformance with the ESCC system and based in the DEVICE information gathered so far and until DEVICE Layout Phase. [D-ASIC, A-ASIC, FPGA, --]

- 1 ESCC Detail Specification is usually needed when the DEVICE undergoes ESCC procurement, evaluation or qualification.

- 2 The final ESCC Detail Specification is consolidated later with additional information acquired during the DEVICE Validation Phase.

DEVICE Layout Phase Review

ECSS-E-ST-20-40_1580122The DEVICE Layout Phase shall be concluded by the DEVICE Layout Phase Review in compliance with requirements from clause 5.1.4. [ALL]

ECSS-E-ST-20-40_1580123The reviewers shall check that any outputs of previous phases that have not been reviewed yet are reviewed and confirmed as ready for the final physical implementation of the DEVICE. [ALL]

For example, if the DEVICE Detailed Design Phase Review was skipped and merged with the DEVICE Layout Phase Review.

ECSS-E-ST-20-40_1580124The following expected outputs shall be reviewed during DEVICE Layout Phase Review: [ALL]

- Layout Generation Report

- Layout Verification Report

- DEVICE Validation Plan (update) (DVaP) as in DRD in Annex D

- DEVICE Radiation Test Plan

- DEVICE Data Sheet (update) as in DRD in Annex H

- ESCC Detail Specification (preliminary)

- DEVICE database (update)

- DEVICE VCD (update)

- DEVICE Feasibility and Risk Assessment Report (update) (DFRAR) as in DRD in Annex F

DEVICE Implementation Phase

Overview

In the DEVICE Implementation Phase the final ASIC DEVICE is manufactured, packaged and prototypes go through Production Tests, the final FPGA DEVICE is programmed, or the final IP Core is implemented in a selected technology, in compliance with DEVICE Development Plan. The phase concludes by the delivery of the tested DEVICEs which undergo validation and customer acceptance in the DEVICE Validation, Qualification and Acceptance Phase, and with the DEVICE Implementation Phase Review.

Production and test

ECSS-E-ST-20-40_1580125Tasks specified in requirements 5.7.2b to 5.7.2e shall be performed and documented by the supplier in an ASIC Production Tests Report, for ASICs, and an FPGA Programming Test Report for FPGAs. [D-ASIC, A-ASIC, FPGA, --]

ECSS-E-ST-20-40_1580126The committed number of DEVICEs using the technology choices specified in the DEVICE Development Plan of DRD in Annex B and DEVICE Requirements Specification of DRD in Annex A shall be manufactured, for ASIC, or programmed, for FPGA. [D-ASIC, A-ASIC, FPGA, --]

ECSS-E-ST-20-40_1580127ASIC Production Tests shall be performed on the ASIC batch agreed between customer and supplier used for the validation tests during the DEVICE Validation, Qualification and Acceptance Phase in compliance with DEVICE Validation Plan specified in the DRD of Annex D. [D-ASIC, A-ASIC, --, --]

ECSS-E-ST-20-40_1580128FPGA Programming Test shall be performed on the same devices used for the validation tests during the DEVICE Validation, Qualification and Acceptance Phase. in compliance with DEVICE Validation Plan as per DRD Annex D. [--, --, FPGA, --]

ECSS-E-ST-20-40_1580129The supplier shall generate the FPGA Programming Test Report including the following: [--, --, FPGA, --]

- FPGA programming steps indicating compliance to the FPGA technology provider's "FPGA programming guidelines".

- Input and output files, specifying the format, identifier, version of netlist files, checksum and bit stream files used and generated during programming.

- HW and SW equipment used.

- The exact FPGA device part used, including serial number and date code.

DEVICE Database update

ECSS-E-ST-20-40_1580130Files generated during the DEVICE Implementation Phase shall be added to the DEVICE Database. [D-ASIC, A-ASIC, FPGA, --]

- 1 For example, new FPGA bit stream files for the final FPGA technology.

- 2 Expected outputs of the DEVICE Implementation phase are the ASIC Production Tests Report or FPGA Programming Test Report, all files used during the production or programming tests and the agreed number of tested DEVICEs.

DEVICE Validation Plan completion

ECSS-E-ST-20-40_1580131The final DEVICE Validation Plan shall be completed as per Annex D in order to start the DEVICE validation test procedures in the following phase. [ALL]

DEVICE Implementation Phase Review

ECSS-E-ST-20-40_1580132The DEVICE Implementation Phase shall be concluded by the DEVICE Implementation Phase Review in compliance with requirements from clause 5.1.4. [ALL]

ECSS-E-ST-20-40_1580133The following expected outputs shall be reviewed during DEVICE Implementation Phase Review: [ALL]

- DEVICE Validation Plan (final) (DVaP) as in DRD in Annex D

- DEVICE Radiation Test Plan (final)

- ASIC Production Tests Report or

- FPGA Programming Tests Report

- DEVICE Data Sheet (update) as in DRD in Annex H

- ESCC Detail Specification (update)

- DEVICE database (update)

- DEVICE VCD (update)

- DEVICE Feasibility and Risk Assessment Report (update) (DFRAR) as in DRD in Annex F

- Agreed number of tested DEVICEs

DEVICE Validation, Qualification and Acceptance Phase

Overview

This is the last phase of the development of the DEVICE. The manufactured or programmed parts which already went through Production Tests, in case of ASICs, or Programming Test, in case of FPGAs, now undergo validation test procedures, as defined in the DEVICE Validation Plan, and if agreed with the customer, radiation tests too. Sometimes these validation tests help to uncover problems or defects in the DEVICE technology provided by the ASIC manufacturer or the DEVICE technology provider. Sometimes the validation tests find design problems that were unfortunately not detected by verification due to tools or design kits limitations or not exhaustive verification coverage. With the data measured in all these tests, the existing versions of the DEVICE user and procurement documents, as agreed with the customer, are corrected and completed by the supplier. The DEVICE Validation, Qualification and Acceptance Phase Review, once declared successful, constitutes the acceptance by the customer of the outputs contractually agreed as deliverables.

In some cases, contractually agreed deliverables can include some of the expected output hardware such as validation tests boards, and software used for the validation test procedures.

DEVICE validation

ECSS-E-ST-20-40_1580134Tasks specified in requirements 5.8.2b to 5.8.2f shall be performed and documented by the supplier in the DEVICE Validation Report. [ALL]

ECSS-E-ST-20-40_1580135The DEVICE validation test procedures shall be performed in compliance with the DEVICE Validation Plan specified in DRD Annex D. [ALL]

ECSS-E-ST-20-40_1580136The supplier shall design and build the validation tests set-up representative of the intended system application environment as defined in the DEVICE Validation Plan. [ALL]

ECSS-E-ST-20-40_1580137The supplier shall use the validation tests set-up to perform validation test procedures that cover all requirements in compliance with DEVICE Validation Plan. [ALL]

Requirements validated include functional, electrical, environmental, test modes and stress conditions.

ECSS-E-ST-20-40_1580138If agreed with the customer and planned in the DEVICE Validation Plan, the supplier shall perform ESCC evaluation or qualification tests. [D-ASIC, A-ASIC, FPGA, --]

For example, as defined in ESCC 9000 specifications: burn-in, V/T stress tests or screening tests.

ECSS-E-ST-20-40_1580139If agreed with the customer and according to the DEVICE Radiation Test Plan, the supplier shall perform radiation test procedures and document the results in the DEVICE Radiation Test Report. [ALL]

DEVICE Support and Maintenance

ECSS-E-ST-20-40_1580140The final DEVICE Support and Maintenance Plan shall be agreed with the customer and produced by the supplier in compliance to DRD in Annex E. [ALL]

ECSS-E-ST-20-40_1580141Any support and maintenance activities done during this phase shall be logged in predefined formats and retained in maintenance records. [ALL]

Experience Summary Report

ECSS-E-ST-20-40_1580142If agreed with the customer, an Experience Summary Report shall be generated in compliance with DRD in Annex I. [ALL]

Final versions of application and procurement documents

ECSS-E-ST-20-40_1580143If agreed with the customer, the final ESCC Detail Specification shall be updated based on the validation test results. [D-ASIC, A-ASIC, FPGA, --]

ECSS-E-ST-20-40_1580144For DEVICEs that are used as off-the-shelf products the final DEVICE Data Sheet shall be updated based on the validation test results. [ALL]

ECSS-E-ST-20-40_1580145If agreed with the customer, a DEVICE User Manual document shall be established in order to guide DEVICE users through different electrical and functional configurations of the DEVICE in typical system applications. [ALL]

For example, describing suitable bias circuitry, supply voltages and configuration modes for typical use scenarios.

DEVICE Validation, Qualification and Acceptance Phase Review

ECSS-E-ST-20-40_1580146The DEVICE Validation, Qualification and Acceptance Phase shall be concluded by the DEVICE Validation, Qualification and Acceptance Phase Review in compliance with requirements from clause 5.1.4. [ALL]

ECSS-E-ST-20-40_1580147The reviewers shall review expected outputs of DEVICE Implementation Phase, in addition to all the expected outputs of this DEVICE Validation, Qualification and Acceptance Phase. [ALL]

ECSS-E-ST-20-40_1580148The reviewers shall check that the DEVICE meets all functional, performance, interface and other requirements in compliance with the DEVICE Requirements Specification as per DRD Annex A. [ALL]

ECSS-E-ST-20-40_1580149The reviewers shall check that preventive measures or contingency plans exist for all identified risk items reported in the DFRAR, including any new ones identified in the Validation, Qualification and Acceptance Phase, in order to accept the identified risks prior to: [ALL]

- DEVICE acceptance by the customer

- FM production, if planned. ECSS-E-ST-20-40_1580150The following expected outputs shall be reviewed during DEVICE Validation, Qualification and Acceptance Phase Review: [ALL]

- Agreed number of tested and validated DEVICEs

- DEVICE Validation Report

- DEVICE Radiation Test Report

- DEVICE Feasibility and Risk Assessment Report (final) (DFRAR) as in DRD in Annex F

- DEVICE Support and Maintenance Plan (final) (DSMP) as in DRD in Annex E

- Experience Summary Report as in DRD in Annex I

- DEVICE Data Sheet (final) as in DRD in Annex H

- ESCC Detail Specification (final)

- DEVICE User Manual

- Validation Tests hardware and software

- DEVICE Database (final)

- DEVICE VCD (final).

Pre-tailoring according to DEVICE criticality and type

DEVICE criticality categories

Criticality categories are assigned to DEVICE products as specified in ECSS-Q-ST-30 clause 5.4 which specifies the relationship between the criticality category of the DEVICE products, the highest criticality of the functions implemented by the DEVICE and the existing system compensating provisions.

To any DEVICE described in the second right column of Table 61 the corresponding criticality category in the left column is assigned. Dependability and safety consequences associated to each DEVICE criticality as per ECSS-Q-ST-30 Table 5-1 are also indicated in Table 61 below.

Table 61: DEVICE criticality categories

|

DEVICE criticality category

|

Definition

|

Dependability consequences

|

Safety consequences

|

|

A |

DEVICE involved in category I functions

|

Failure propagation (Only for lower than system level analysis) (refer to requirement 5.3.2.c of ECSS-Q-ST-30)

|

Loss of life, life-threatening or permanently disabling injury or occupational illness Loss of system Loss of an interfacing manned flight system Loss of launch site facilities Severe detrimental environmental effects |

|

DEVICE included in compensating provisions for category I functions

| |||

|

B |