Space product assurance

Design rules for printed circuit boards

Foreword

This Standard is one of the series of ECSS Standards intended to be applied together for the management, engineering and product assurance in space projects and applications. ECSS is a cooperative effort of the European Space Agency, national space agencies and European industry associations for the purpose of developing and maintaining common standards. Requirements in this Standard are defined in terms of what shall be accomplished, rather than in terms of how to organize and perform the necessary work. This allows existing organizational structures and methods to be applied where they are effective, and for the structures and methods to evolve as necessary without rewriting the standards.

This Standard has been prepared by the ECSS-Q-ST-70-12C Working Group, reviewed by the ECSS Executive Secretariat and approved by the ECSS Technical Authority.

Disclaimer

ECSS does not provide any warranty whatsoever, whether expressed, implied, or statutory, including, but not limited to, any warranty of merchantability or fitness for a particular purpose or any warranty that the contents of the item are error-free. In no respect shall ECSS incur any liability for any damages, including, but not limited to, direct, indirect, special, or consequential damages arising out of, resulting from, or in any way connected to the use of this Standard, whether or not based upon warranty, business agreement, tort, or otherwise; whether or not injury was sustained by persons or property or otherwise; and whether or not loss was sustained from, or arose out of, the results of, the item, or any services that may be provided by ECSS.

Published by: ESA Requirements and Standards Division ESTEC, P.O. Box 299, 2200 AG Noordwijk The NetherlandsCopyright: 2014© by the European Space Agency for the members of ECSS## Change log

|

ECSS-Q-ST-70-12C

|

First issue

|

Introduction

PCBs are used for the mounting of electronic components to produce PCB assemblies that perform electrical functions. The PCBs are subjected to thermo‐mechanical stress during assembly such as soldering of components, rework and repair under normal terrestrial conditions. In addition the assembled PCBs are exposed to the launch and space environment. The reliability of the circuit depends on the robustness of the design, among other factors. Moreover, PCB design with high technological complexity enables the use of complex components with advanced functionality.

Scope

This standard specifies the requirements for the supplier and PCB manufacturer for PCB design.

This standard is applicable for all types of PCBs, including sequential, rigid and flexible PCBs, HDI and RF PCBs.

This standard can be made applicable for other products combining mechanical and electrical functionality using additive or reductive manufacturing processes, as used in PCB manufacturing. Examples of such products are slip rings and bus bars.

This standard may be tailored for the specific characteristics and constraints of a space project in conformance with ECSS-S-ST-00.

Normative references

The following normative documents contain provisions which, through reference in this text, constitute provisions of this ECSS Standard. For dated references, subsequent amendments to, or revision of any of these publications do not apply. However, parties to agreements based on this ECSS Standard are encouraged to investigate the possibility of applying the more recent editions of the normative documents indicated below. For undated references, the latest edition of the publication referred to applies.

|

ECSS-S-ST-00-01

|

ECSS system – Glossary of terms

|

|

ECSS-Q-ST-70-02

|

Space product assurance - Thermal vacuum outgassing test for the screening of space materials

|

|

ECSS-Q-ST-70-08

|

Space product assurance - Manual soldering of high-reliability electrical connections

|

|

ECSS-Q-ST-70-10

|

Space product assurance - Qualification of printed circuit boards

|

|

ECSS-Q-ST-70-11

|

Space product assurance - Procurement of printed circuit boards

|

|

ECSS-Q-ST-70-38

|

Space product assurance -High-reliability soldering for surface-mount and mixed technology

|

|

ECSS-E-ST-20

|

Space engineering – Electrical and electronic

|

|

ECSS-E-ST-20-06

|

Space engineering - Spacecraft charging

|

|

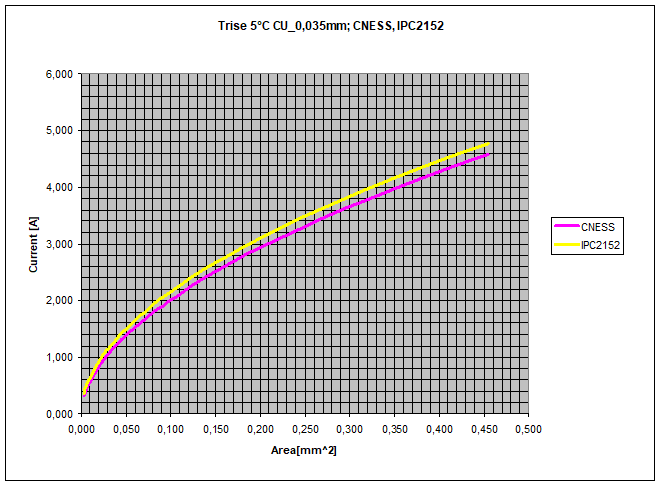

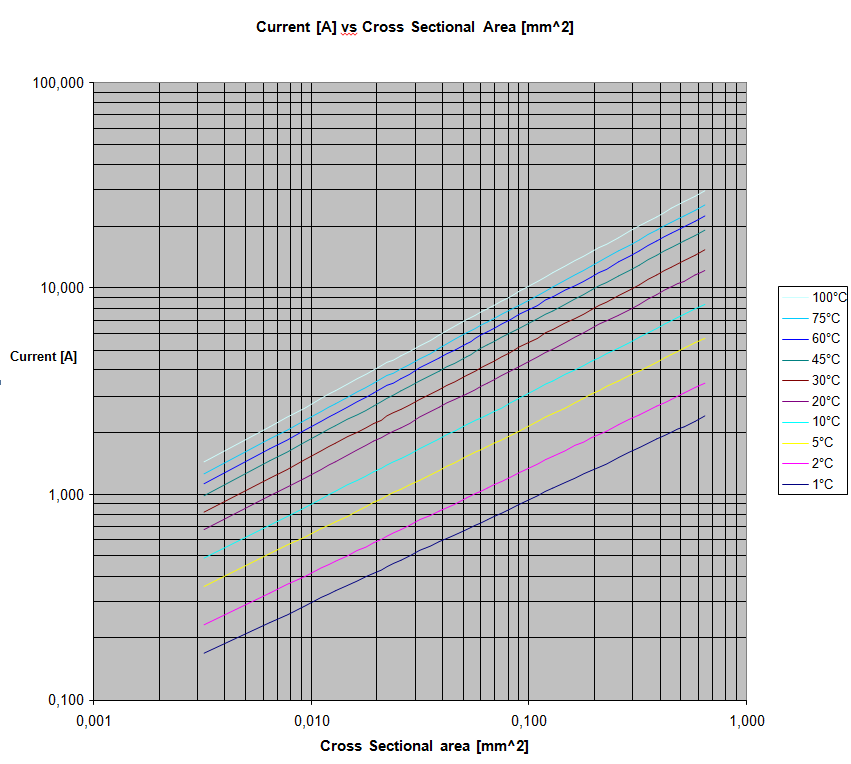

IPC-2152, August 2009

|

Standard for determining current carrying capacity in printed board design

|

|

IPC-4101D, April 2014

|

Specification for base materials for rigid and multilayer printed boards

|

|

IPC-4562A, April 2008

|

Metal foil for printed wiring applications

|

Terms, definitions and abbreviated terms

Terms from other standards

For the purpose of this Standard, the terms and definitions from ECSS-S-ST-00-01 apply, and in particular for the following terms:

supplier

In the context of this standard the supplier is also responsible for the design of the PCB.

Terms specific to the present standard

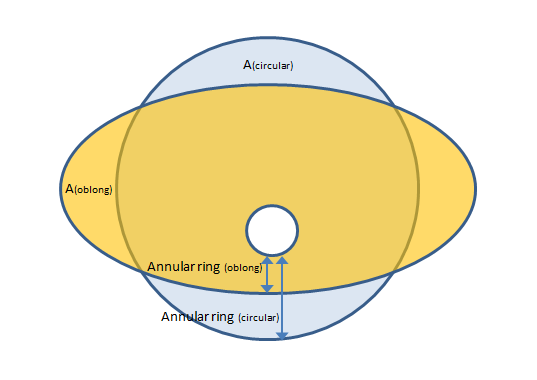

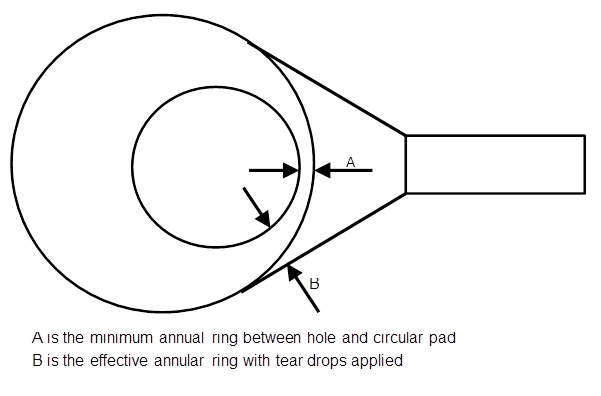

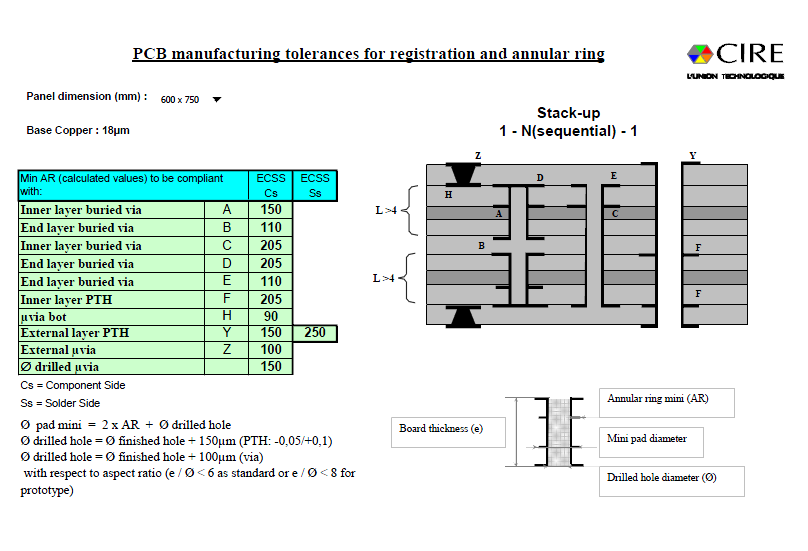

annular ring

ring of copper pad surrounding the drilled hole

The measurement of annular ring is different on internal and external layers. See clause 6.3.1 from ECSS-Q-ST-70-11.

area array device (AAD)

surface mount package wherein the solder terminations are formed in a grid on the bottom of the package

BGA and CGA are specific types of AAD.

artwork

graphical representation of individual layers

Examples of artwork are: conductive layers, solder mask, silk screen, selective finishes, heat sink.

as-designed

state of the PCB in the design phase

This typically refers to dimensions associated with the designed PCB, which does not take into account manufacturing tolerances.

as-manufactured

state of the PCB after manufacturing

This typically refers to dimensions measured on the manufactured PCB, the final product. The dimensions are measurements that include manufacturing tolerances.

as-manufactured hole

hole in as-manufactured PCB after all process steps

In case of a plated through-hole, an as-manufactured hole includes plating and surface finish.

aspect ratio

ratio of the as-designed thickness of the build-up and the diameter of the drilled hole

assembled PCB

PCB with all its electronic and mechanical components mounted, having undergone all the manufacturing operations

Examples of manufacturing operations are wiring, soldering, wire-bonding, gluing, screwing, potting and conformal coating.

assembly house

company performing assembly of PCB

back-drilled hole

via with part of its metallisation removed on one side by depth controlled mechanical drilling with a larger diameter drill

ball grid array (BGA)

surface mount package wherein the solder balls for terminations are formed in a grid on the bottom of the package

BGA is a specific type of AAD.

basic copper

copper foil layer that excludes etching and plating steps

blind via

type of via exposed only on one side of the PCB

One method to manufacture a blind via can be by depth controlled drilling. A second method can be by sequential lamination of minimum 2 half-stacks.

bondply

type of cover layer with adhesive on both sides for the purpose of bonding flex laminate

Bondply is a trademark manufactured by DuPont.

build-up

technical representation of individual conductive layers and dielectric materials of the specific PCB design

Examples of a build-up are given in Figure 31 and Figure A-4

buried via

type of via connecting internal layers without being exposed on either surface

column grid array (CGA)

surface mount package wherein the columns for terminations are formed in a grid on the bottom of a package

CGA is a specific type of AAD.

conductive layer

electrically conductive parts of a PCB on the same layer

The conductive layer can contain tracks, planes or pads.

conductor

conductive elements within the PCB

Elements within the conductive layer and vias are conductors.

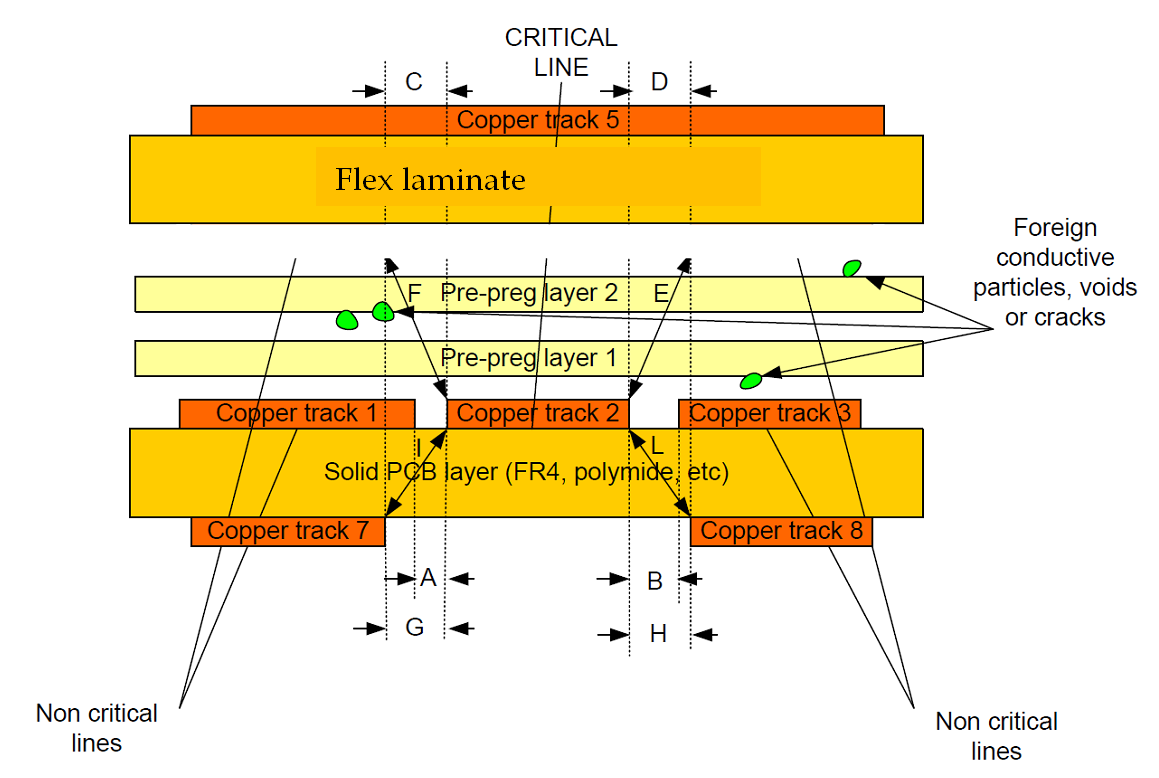

critical net

conductive circuit with a specific functionality that requires redundant solutions to avoid loss of functionality in case of any credible single failure

Redundant solutions can be double insulation, increased copper cross section, multiple vias.

critical track

track that is part of a critical net

double insulation

barrier between tracks or elements of an electronic circuit that provides insulation of tracks or elements of an electronic circuit in case of any credible single failure

drilled hole

hole after drilling and before plating

In case of a plated through-hole, drilled hole excludes plating and surface finish

electrical field

voltage per insulation distance between two conductors

This is a simplified representation of electrical field applicable for PCB design.

fine pitch

spacing of tracks or pads that is more dense than for normal pitch

The exact perimeter of fine pitch on external and internal layers is described in clause 7.4.

FR4

type of laminate and prepreg with a specific epoxy resin

half-stack

sequence of laminated layers that are included in further lamination sequences to form the finished PCB

heat sink

layer of thick metal with the purpose of thermal dissipation internal or external of the PCB

Term “thermal drain” is synonymous with the word “heat sink”.

high density interconnect (HDI)

technology on PCB related to the pattern that allows a smaller pitch in the footprint on the surface pattern and a higher density of internal signal routing than for conventional PCBs

- 1 The exact perimeter of HDI technology is described in clause 11.

- 2 This technology can be required for assembly of AAD.

- 3 An example of HDI build-up is shown in Figure 31.

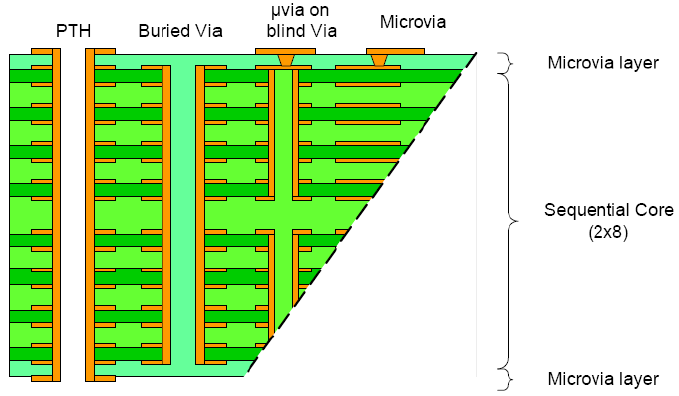

Figure 31: Simplified build-up of HDI PCB

Figure 31: Simplified build-up of HDI PCB

high speed signal

electronic functionality that requires specific design precautions to maintain time dependant signal integrity

This is further specified in IPC-2251 and IPC-2141A.

hole wall pull away

adhesion defect between copper of the hole wall and resin

HTE

grade of copper foil with the grade designation “high temperature elongation electrodeposited”

This is specified in IPC-4562A.

intralayer

within the same layer in X,Y direction

interlayer

in between two superpositioned layers in Z direction

JTC

grade of copper foil

This grade of copper foil is produced by GOULD Electronics GmbH.

laminate

sheets of fully cured, C-stage, resin with copper cladding

Rigid laminate includes reinforcement, for example by woven glass fibres or non-woven aramid fibres.

microvia

blind via manufactured by laser ablation with a diameter smaller than conventional vias.

- 1 Microvias are required for routing internal signals in HDI PCBs.

- 2 Example of microvia configuration is shown in Figure 31.

microvia layers

layers of conductive pattern that contain microvias

microvia layers are layers 1 and 2 and opposite layers

mil

unit of length equal to 25,4 µm

The unit mil is in some cases customary in PCB design and therefore preferred above the SI unit.

no-flow prepreg

type of prepreg that has a reduced flow of resin during press cycle

The term “low-flow prepreg” is synonymous with the word “no-flow prepreg”. The terms do not specify the exact amount of flow.

non-functional pad

pad on internal copper layer without electrical connection

non-plated hole

hole in a PCB that does not contain plating or other type of conductive reinforcement

normal pitch

standard spacing of tracks and pads

See “fine pitch” for another category of pitch.

number of layers

number of layers in a PCB containing conductive elements

* For example, the numbering convention is from top to bottom layer: L1, L2, …,Ln-1, Ln.

panel

area of laminated layers that contains PCBs and coupons processed as a single unit

PCB manufacturer

entity that manufactures the PCB

peelable

areas of photo resist or copper that have poor adhesion to underlying substrate because of a tapered shape with a narrow dimension on one end

plated through-holes (PTH )

metal-plated holes drilled through all the layers used for assembly of components

printed circuit board (PCB)

product resulting from the process of selectively etching unwanted copper from surfaces of copper clad insulating substrates to form a desired circuitry pattern which is metal-plated and laminated

Examples of specific PCB technologies are rigid, flexible, rigid-flex, double sided, multilayer, sequential, RF and HDI PCBs

prepreg

sheets of partly cured, B-stage, resin with reinforcement

Examples of reinforcement are woven glass fibres and non-woven aramid fibres.

RF elements

conductive pattern on PCB with specific RF functionality

For example filters, combiners, splitters, couplers. RF elements do not have voltage ratings or solder connections.

resin starvation

region in a PCB that has an insufficient amount of resin to wet out completely the reinforcement

This is shown by low gloss, dry spots or exposed fibres.

review item

design feature to be included into the PCB definition dossier and reviewed during the PCB design review

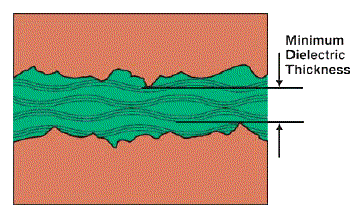

projected peak-to-peak insulation distance

worst-case minimum thickness of dielectric material that includes thickness tolerance of the laminate core and the maximum roughness of copper surface treatment

Figure 32 specifies how this is measured.

Figure 32: Projected peak-to-peak insulation distance

Figure 32: Projected peak-to-peak insulation distance

serialization

process of numbering of each unique PCB by the PCB manufacturer for traceability

sliver

pieces of photo resist or copper that have poor adhesion to underlying substrate because of the small surface area.

For example, a surface area below 0,01 mm2

soldering pad

conductive part intended for soldering components on the PCB

spacing

insulation distance

The term “gap” is synonymous with the word “spacing”, but this term is not used in the present standard.

stack

assembly comprising of one sequence of laminated layers

Half-stack identifies the sub-assembly.

test pad

pad that is dedicated for electrical testing on the PCB

track

conductive part routing the electrical connection between the pads

The term “line” and the term “conductive track” are synonyms with the word “track”

via

metal-plated hole drilled through all layers, only used for interconnection between layers

A via is not used for assembly

X,Y direction

orientation in the plane of the PCB, along length and width of the PCB

Z direction

orientation perpendicular to the plane of the PCB, along height of the PCB

Abbreviated terms

For the purpose of this Standard, the abbreviated terms from ECSS-S-ST-00-01 and the following apply:

|

Abbreviation

|

Meaning

|

|

AAD

|

area array device

|

|

AC

|

alternating current

|

|

AOI

|

automated optical inspection

|

|

BGA

|

ball grid array

|

|

CAD

|

computer aided design

|

|

CAE

|

computer aided engineering

|

|

CGA

|

column grid array

|

|

CIC

|

Copper – Invar - Copper

|

|

CoC

|

certificate of conformance

|

|

CRC

|

cyclic redundancy check

|

|

CTE

|

coefficient of thermal expansion

|

|

Cu

|

copper (element)

|

|

DC

|

direct current

|

|

DRD

|

document requirements definition

|

|

DWV

|

dielectric withstanding voltage

|

|

GND

|

electrical signal to ground

|

|

EMC

|

electromagnetic compatibility

|

|

FAI

|

first article inspection

|

|

FP

|

flat pack

|

|

FR4

|

type of epoxy resin for PCBs

|

|

HDI

|

high density interconnect

|

|

i.a.w.

|

in accordance with

|

|

I/O

|

input/output

|

|

LCC

|

leadless chip carrier

|

|

LF

|

low frequency

|

|

MRR

|

manufacturing readiness review

|

|

PCB

|

printed circuit board

|

|

PID

|

process identification document

|

|

ppm

|

parts per million (10-6)

|

|

PTH

|

plated through hole

|

|

PTFE

|

polytetrafluoroethylene

|

|

QFP

|

quad flat pack

|

|

RF

|

radio frequency (high frequency)

|

|

SOIC

|

small outline integrated circuits

|

|

SPF

|

single point failure

|

|

sq

|

square (in unit Ω/sq)

|

|

TDR

|

time domain reflectometry

|

|

Tg

|

temperature of glass transition

|

|

Th

|

thickness

|

|

Vcc

|

power supply voltage

|

|

Vrms

|

voltage root mean square

|

Principles

Qualified PCBs

Qualified PCBs for space application meet the following conditions:

PCB is procured in conformance with requirements of ECSS-Q-ST-70-11,

PCB is procured from a PCB manufacturer that is qualified in conformance with requirements of ECSS-Q-ST-70-10,

the PCB technology is qualified in conformance with requirements of ECSS-Q-ST-70-10 for that PCB manufacturer,

the PCB design is in conformance with the requirements of ECSS-Q-ST-70-12, and

the PCB design, the manufacturing process and materials are in conformance with the PID of the PCB manufacturer.

PA requirements of space projects use this standard as applicable document. Based on their heritage, suppliers can propose the re-use of existing PCB designs that are “recurrent” and that are not in compliance with all design requirements of this standard. The possible acceptability of those cases is reviewed by the project on case by case basis. The PCB design is “recurrent” only when no changes are made in the artwork, routing, lay-out, build-up, material selection.

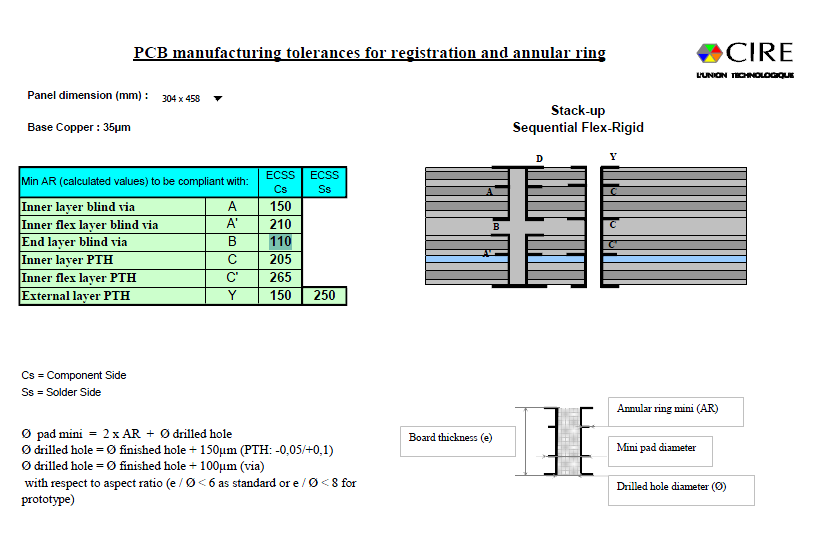

Manufacturing tolerances

Dimensional measurements of PCBs are “as-designed” except when explicitly mentioned “as-manufactured”.

Design values are affected by the manufacturing tolerances. The minimum value on the PCB as-manufactured equals the design value subtracted with the manufacturing tolerance. See definition of terms in clause 3.2.

Reliability of design

Specific design features of PCBs are recorded as Review Items in the PCB definition dossier. This is done when the design features include a higher technological complexity that can affect manufacturability or (thermal) reliability. These design features are specifically evaluated by qualification prior to inclusion in the PID.

Requirements in this standard generally state minimum dimensions permitted. It is good practice to use minimum dimensions only when necessary to achieve the desired functionality and to design with margin when possible. For instance, it is recommended to implement minimum insulation distance between tracks only when space limitations prevent larger insulation distance. It is recommended to implement fan out of tracks which allows for larger insulation distances where more space is available.

The robustness of the PCB can be affected when combining multiple design features at the limit of the requirement or recorded as Review Item. The PCB manufacturer and the supplier evaluate this risk during the design review and provide formal approval during the MRR. The reliability of the manufactured PCB is evaluated by inspection on representative coupons.

Design review and MRR

Overview

This clause specifies the iterative process of designing a PCB in collaboration with the PCB manufacturer and specifies associated documentation for the formal authorization for manufacture.

Documentation

The supplier shall issue the PCB definition dossier in conformance with the DRD in Annex A.

The supplier shall list design features as Review Items in conformance with clause A.2.1<7> from the DRD of the Annex A.

The supplier may list other design features as Review Items .

The supplier shall submit the PCB definition dossier to the PCB manufacturer for the design review.

The supplier should submit to the PCB manufacturer the draft PCB definition dossier or a list of specific Review Items specified in the requirement 5.2b in the design phase, when those Review Items are at the limit of the PID capability.

Examples of Review Items that can be on the limit of PID capability are: dimensions, number of layers, maximum aspect ratio, number of sequences, material selection or a combination of these. Consultation with PCB manufacturer at this early design stage is recommended to avoid unnecessary risks. Multiple iterations can be performed to achieve an agreed PCB definition dossier.

The PCB manufacturer shall review the PCB definition dossier including Review Items for compliance with the PID.

As a result of the design review, the PCB manufacturer may identify to the supplier additional Review Items in the PCB definition dossier.

Review Items can exist for PCB designs even within the capability of the PID. These Review Items and methods to mitigate them are specified in this standard as best practices and recommendations.

The PCB manufacturer shall provide the PCB manufacturing dossier in conformance with DRD in the Annex B.

The PCB manufacturer shall issue to the supplier a MRR checklist, which is part of the PCB manufacturing dossier, in conformance with the DRD in the Annex B.

An example of a MRR checklist is given in Annex G.

During the MRR, supplier and PCB manufacturer shall approve the PCB manufacturing dossier, the PCB definition dossier and all Review Items.

The approvals are recorded in the MRR checklist.

The MRR shall provide authorisation for manufacture to the PCB manufacturer.

General design and production requirements

Reliability of design

The supplier shall design the PCB with margin.

This is also described in clause 4.3.

Choice of materials and build-up

Overview

For the selection of materials for PCB a number of physical properties are important, such as Tg, Young’s modulus, dielectric constant, CTE, hygroscopy. Table 61 provides an overview of some commonly used materials and their physical properties. The CTE of the as-manufactured PCB depends on the total copper thickness, which has a CTE of about 16 ppm/K.

It is important that for the selection of the technology for the PCB design the following is taken into account:

CTE mismatch between devices and PCB,

moisture sensitivity of PCB function,

interconnection constraints,

lay-out constraints.

Rigid-flex boards can be preferred to reduce the interconnection constraints.

Polyimide and epoxy are the most commonly used materials. Polyimide has an advantage over epoxy because it is more thermally stable and outperforms epoxy in thermal cycling and assembly. At the same time, polyimide is more hygroscopic than epoxy, which affects PCB ground use and assembly. Epoxy is available with different glass transition temperatures (Tg). Higher glass transition temperature is recommended for epoxy because it provides better thermal stability. Thermal expansion of resin in Z direction below and above Tg is typically higher than expansion of copper. Therefore it is beneficial for thermal endurance to use materials with low CTE in Z direction. Flame retardants in base materials are commonly required for ground based applications but are not necessary for space based PCBs.

For high frequency performance typically PTFE based materials are used. These materials require special lamination cycles as adhesion is generally poorer compared to polyimide and epoxy.

IPC-4121 provides a comparison of various properties for core constructions as function of resin and glass type.

Table 61: Characteristics of some example dielectric materials for laminates

|

Type of material

|

Dielectric constant

|

Dissipation Factor

|

Tg (°C)

|

water absorption (%)

|

Volume density (g/cm3)

|

CTE (ppm/K)

|

CTE (ppm/K)

|

Thermal conductivity (W/m.K)

|

Example

| ||||||

|

at 1 MHz

|

at 10 GHz

|

at 1 MHz

|

at 10 GHz

|

|

|

|

X

|

Y

|

Z

|

X

|

Y

|

Z

|

|

|

|

|

Epoxy HTg

|

4,24

|

3,92

|

0,015

|

-

|

180

|

0,15

|

-

|

13 - 14

|

13 - 14

|

45

|

14 - 17

|

14 - 17

|

230

|

0,4

|

370 HR

|

|

4,24

|

3,92

|

0,015

|

-

|

170

|

0,15

|

-

|

13 - 14

|

13 - 14

|

45

|

14 - 17

|

14 - 17

|

230

|

0,4

|

IS420 (Isola)

| |

|

Polyimide / Glass

|

4,2

|

-

|

0,01

|

-

|

> 250

|

0,26

|

1,6

|

16

|

16

|

51

|

-

|

-

|

158

|

0,2

|

35N (Arlon)

|

|

4,2

|

-

|

0,01

|

-

|

250

|

0,27

|

1,6

|

16

|

16

|

55

|

-

|

-

|

149

|

0,2

|

85N (Arlon)

| |

|

Polyimide / Aramid

|

3,6

|

-

|

0,014

|

-

|

250

|

0,6

|

1,37

|

6 - 9

|

6 - 9

|

93

|

-

|

-

|

279

|

0,2

|

85NT (Arlon)

|

|

Polyimide flex laminate

|

3,4

|

3,3

|

0,003

|

-

|

220

|

0,8

|

-

|

25

|

25

|

-

|

-

|

-

|

-

|

-

|

AP (DuPont)

|

|

Ceramic reinforced PTFE

|

-

|

2,94

|

-

|

0,0012

|

-

|

0,02

|

2,1

|

16

|

16

|

24

|

-

|

-

|

-

|

0,6

|

RT/Duroid 6002 (Rogers)

|

|

Hydrocarbon and ceramic reinforced glass

|

-

|

3,38

|

-

|

0,0027

|

> 280

|

0,06

|

1,79

|

11

|

14

|

46

|

-

|

-

|

-

|

0,71

|

RO 4003 (Rogers)

|

|

Glass reinforced PTFE

|

2,20

|

2,20

|

0,0004

|

0,0009

|

-

|

0,02

|

2,2

|

31

|

48

|

237

|

-

|

-

|

-

|

0,2

|

RT/Duroid 5880 (Rogers)

|

|

Ceramic thermoset

|

-

|

9,8

|

-

|

0,002

|

-

|

0,16

|

2,77

|

19

|

19

|

20

|

-

|

-

|

-

|

0,76

|

TMM10i (Rogers)

|

Material selection

Selection of the base laminate materials shall be performed in compliance with the requirements from the clause 5.2.1 of the ECSS-Q-ST-70-11.

The material selection for all types of PCBs shall be in compliance with the requirements from the clauses 7.1 to 7.6 of the ECSS-Q-ST-70-11.

Examples of types of PCBs are: single sided, double sided, multilayer, sequential, rigid, rigid-flex, flexible, sculptured flex, HDI, RF.

The as-manufactured PCB shall be in conformance with the outgassing requirements of the clause 5.5.3 from the ECSS-Q-ST-70-02 or project specific requirements on cleanliness.

The outgassing requirements are CVCM<0,1% and RML<1,0%.

Selection of the PCB manufacturer

The supplier shall procure PCBs from a PCB manufacturer with a qualification approval for an identified technology in conformance with the requirements from the clause 5 to clause 9 of the ECSS-Q-ST-70-10.

The supplier shall procure the PCBs in conformance with the requirements from the clause 5 to clause 7 of the ECSS-Q-ST-70-11.

Traceability and marking

The PCB shall be marked with part number and revision number from the PCB definition dossier as given by the supplier.

All individual PCBs within the panel shall be identified by a serial number.

The serialization of the PCB shall be established before the start of the fabrication.

The serial number shall identify the position of the PCB on the panel.

The serial number methodology shall be identified in the PID of the PCB manufacturer.

Rigid PCBs

PCB build-up

General

The build-up of the PCB and each sub-assembly should be symmetric.

This is done to avoid warp and twist.

The supplier shall record asymmetric build-up as a Review Item in the PCB definition dossier.

The build-up includes the copper thickness and its distribution.

In case Molybdenum or CIC layers are used, they shall be included in the build-up and recorded as a Review Item in the PCB definition dossier.

- 1 Specific requirements for the build-up are listed in the PCB definition dossier in A.2.1<5>a.3(h).

- 2 On external layers, copper clad laminate typically achieves better peel strength whereas copper foil achieves better registration.

Copper styles

The thickness of the copper cladding on both sides of the laminate should be equal except on outer layers of the PCB or half-stack.

Equal copper thickness is needed when laminate is etched in same process steps, as is the case for internal layers. The exception on outer layers is made because each side is etched in different process steps and because thin copper on external layers decreases the total thickness after plating.

In case the thickness of the copper cladding on the laminate is asymmetric, this asymmetric build-up of the PCB shall be recorded as a Review Item in the PCB definition dossier.

17/70 copper thickness is more risky than 17/35 or 35/70 copper thickness. The presence of fine pitch tracks in combination with asymmetric copper further increases the difficulty to process.

Except the case specified in the requirement 11.4.1e, the external and internal layers shall use basic copper thickness 70 µm, 35 µm or 17 µm.

- 1 Copper layers can be implemented as copper clad laminate or as separate copper foils.

- 2 Requirement 11.4.1e specifies microvia layers on HDI PCBS.

Copper distribution within a layer should be homogeneous.

This is done to ensure even pressure distribution during lamination, which can cause filling voids, cracks or glass compression.

Balancing of copper should be performed by including dummy non-functional copper.

This is more important for partial planes on thick copper layers such as 70 µm.

Signal tracks should not be routed on copper plane layers.

In case the total as-designed thickness of copper is above 700 µm, this shall be recorded as a Review Item in the PCB definition dossier.

High layer count in combination with thick copper layers can have significant impact on manufacturability and long-term reliability.

Copper quality “HTE” shall be used for copper clad laminate.

Type HTE can be procured in conformance with IPC-4562 Type E, grade 3.

Copper quality “JTC” or “HTE" shall be used for copper foils.

The values from the Table 71 should be used in the design calculations for copper foil thickness.

The values indicated in Table 71 are minimum as-manufactured thickness for the specified as-designed foil thickness.

Table 71: As-designed versus as-manufactured copper foil thickness

|

As-designed foil thickness

|

Minimum as-manufactured thickness for non-plated inner layers

|

Minimum as-manufactured thickness for plated layers with ≥25 µm plating

|

|

9

|

6

|

31

|

|

12

|

9

|

34

|

|

17

|

11

|

38

|

|

35

|

25

|

53

|

|

70

|

56

|

84

|

Dielectric thickness

A minimum of two sheets of prepreg shall be used for insulation between two layers.

A minimum of two sheets of glass should be used in glass-reinforced laminates.

In case a single sheet of glass is used in a glass-reinforced laminate it shall be recorded as Review Item in the PCB definition dossier.

Two sheets of glass reinforcement are specified to mitigate the risk of reduced insulation caused by contamination. This is also specified for laminates for class 3/A in accordance with IPC-6012 Appendix A. In case a single reinforcement in laminate is used, it is recommended to implement other means to mitigate the risk of contamination in laminate. IPC-4121 provides various properties, such as resin-to-glass ratio, for core laminate constructions.

The insulation distance as-designed between two layers in rigid laminate or prepreg in Z direction should be in conformance with the values from Table 137.

This table specifies a minimum distance of 100 µm.

Except the case specified in the 11.4.1h, the insulation distance as-manufactured between two layers in rigid laminate or prepreg in Z direction shall be in conformance with the values from Table 137.

- 1 This table specifies a minimum projected peak-to-peak distance of 70 µm.

- 2 Requirement 11.4.1h specifies microvia layers on HDI PCBs..

Double-sided copper clad laminate with a thickness as-designed of 4 mil (100 µm) shall not be used unless: - the voltage is less than 30V,

- the copper foil thickness on both sides of the laminate is 17 µm or 35 µm,

- the laminate batch is screened by the PCB manufacturer to have a nominal thickness of the etched laminate of ≥ 3,8 mil,

- the insulation distance as-manufactured is verified by the PCB manufacturer to be in compliance with requirement 7.1.3e, and

- it is recorded as a Review Item in the PCB definition dossier.

- 1 Requirement 7.1.3f.1 is in compliance with the values from Table 133.

- 2 The nominal thickness of etched laminate from the requirement 7.1.3f.3 can be read from the CoC. However, this does not indicate worst-case thickness as mentioned in the requirement 7.1.3e. Therefore the use of 4 mil laminate on the lower end of the tolerance between 3,5 mil and 3,8 mil is prohibited by this requirement.

- 3 The precautions specified in this requirement are defined to prevent a worst-case insulation value of less than 70 µm due to high tolerances with rough copper surface treatment as indicated in Table 72.

Double-sided copper clad laminate with a thickness as-designed of 5 mil (125 µm) shall not be used above 30 V unless: - the thickness of laminate as-manufactured is in conformance with the Table 133,

- the laminate batch is screened by the PCB manufacturer to have a nominal thickness of the etched laminate of ≥ 4,8 mil,

- the as-manufactured insulation distance is verified by the PCB manufacturer to be in compliance with requirement 7.1.3g.1,

- it is recorded as a Review Item in the PCB definition dossier.

- 1 The thickness value of the requirement 7.1.3g.1 is ≥100 µm.

- 2 This value specified in the requirement 7.1.3g.2 can be read from the CoC. It does not indicate worst-case thickness as mentioned in the requirement 7.1.3g.1. This prohibits the use of 5 mil laminate on the lower end of the tolerance between 4,5 mil and 4,8 mil.

- 3 Precautions specified in this requirement are defined to prevent a worst-case insulation value of less than 100 µm due to high tolerances with rough copper surface treatment as indicted in Table 72.

For insulation distance in Z direction of a laminate, the minimum projected peak-to-peak insulation distance specified in the requirement 7.1.3i shall be used.

The minimum projected peak-to-peak insulation distance shall include the thickness tolerance of the laminate core and the maximum roughness of copper surface treatment.

Projected peak-to-peak insulation distance is specified in Figure 3-1 of IPC-4101.

If available, laminates should be class D in conformance with requirements from the IPC-4101 except the cases specified in the requirement 7.1.3k.

- 1 Class D guarantees a minimum projected peak-to-peak insulation distance.

- 2 Typically used materials can be unavailable in class D even though this specification exists.

In case other laminate classes are used, the PCB manufacturer shall calculate minimum projected peak-to-peak insulation distance in conformance with requirement 7.1.3i.

An example of this is shown in Table 72 for class C laminate and commonly used copper profiles.

The PCB manufacturer shall define laminate and prepreg styles and amount to achieve the insulation distances as designed by the supplier in conformance with requirements of the clause 13.8.

The supplier is responsible to design insulation distances required to meet design voltages in conformance with the requirement 13.8.2c.

Table 72: Example of worst case as-manufactured insulation distance for laminate with double-sided copper cladding

|

As-designed laminate thickness

|

Laminate thickness tolerance i.a.w. IPC4101 Table3.7 class C.

|

Copper foil 18 or 35 µm

|

Copper foil 70 µm

| ||

|

“Very low profile” i.a.w. IPC4562 Table3.1

|

Worst-case as-manufactured projected peak-to-peak insulation distance

|

“Low profile” i.a.w. IPC4562 Table3.1

|

Worst-case as-manufactured projected peak-to-peak insulation distance

| ||

|

101,6 µm

|

±13 µm

|

5,1 µm

|

78,4 µm

|

10,2 µm

|

68,2 µm

|

|

127 µm

|

±18 µm

|

5,1 µm

|

98,8 µm

|

10,2 µm

|

88,6 µm

|

|

152 µm

|

±18 µm

|

5,1 µm

|

123,8 µm

|

10,2 µm

|

113,6 µm

|

|

203 µm

|

±25 µm

|

5,1 µm

|

167,8 µm

|

10,2 µm

|

157,6 µm

|

|

254 µm

|

±25 µm

|

5,1 µm

|

218,8 µm

|

10,2 µm

|

208,6 µm

|

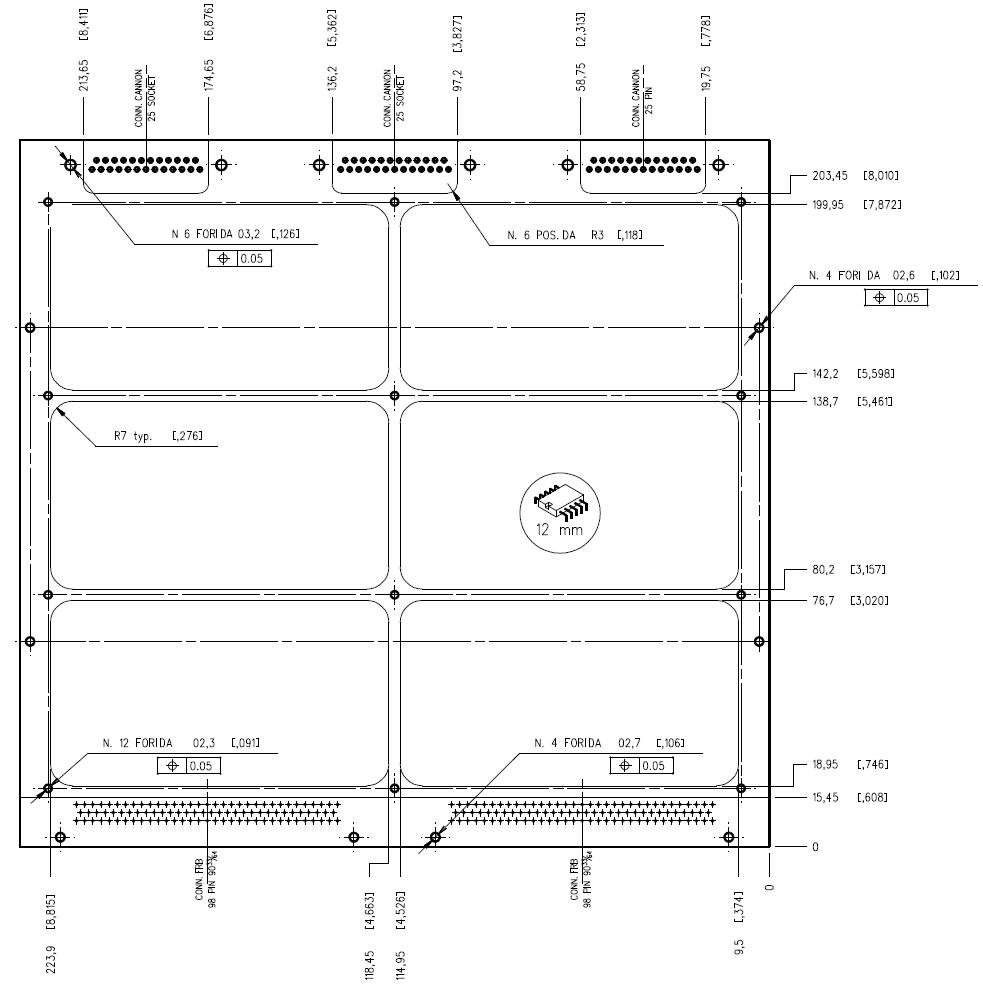

PCB dimension

The maximum dimensions of the PCB depend on the panel dimensions used and qualified by the PCB manufacturer. A typical large panel size is 45x60 cm (18x24 inch). Not all surface area of the panel is available for the PCB design as mandatory coupons are included in the panel.

Thickness of PCB

General

PCB thickness shall be measured from bottom insulation to top insulation.

- 1 The manufacturing tolerance is provided by the PCB manufacturer.

- 2 It is important to include the manufacturing tolerance of 10% in conformance with the requirement 7.6.b.2 from the ECSS-Q-ST-70-11.

- 3 Tolerances on individual copper clad laminate of 100 µm is about ± 18%. Tolerance on the total PCB stack is typically lower.

- 4 Specific requirements for maximum thickness over metal surface finish are specified in the PCB definition dossier.

Polyimide PCB

The thickness as-manufactured of a rigid and rigid-flex polyimide PCB shall be ≤ 4,0 mm.

The as-designed thickness of a rigid and rigid-flex polyimide PCB should be ≤ 3,6 mm, except the case specified in the requirement 7.3.2c.

The as-designed thickness of a rigid and rigid-flex polyimide PCB may be > 3,6 mm in case:

- the thickness as-manufactured is in conformance with requirement 7.3.2a,

- the manufacturing tolerance is < 10%, and

- it is recorded as a Review Item in the PCB definition dossier.

Epoxy PCB

The thickness as-manufactured of a rigid and rigid-flex epoxy PCB shall be ≤ 2,4 mm.

The as-designed thickness of a rigid and rigid-flex epoxy PCB should be ≤ 2,2 mm, except the case specified in the requirement 7.3.3c.

The as-designed thickness of a rigid and rigid-flex epoxy PCB may be >2,2 mm in case:

- the thickness as-manufactured is in conformance with requirement 7.3.3a,

- the manufacturing tolerance is < 10%, and

- it is recorded as a Review Item in the PCB definition dossier.

Number of copper layers in PCB

Number of copper layers for polyimide PCB shall be ≤ 26.

Number of copper layers for epoxy PCB shall be ≤ 20.

Aspect ratio of vias

Except the case specified in the requirement 11.5.6a, the aspect ratio of vias on a rigid and rigid-flex PCB shall be ≤ 7.

- 1 There is no additional requirement for the minimum diameter of plated via in case the diameter conforms to the aspect ratio of ≤ 7.

- 2 Requirement 11.5.6a specifies aspect ratio for AAD with 1 mm pitch on HDI PCBs.

Track width and spacing

General

A verification should be performed to prevent non-functional changes of direction of tracks.

Some automated routing software can cause unnecessary changes of direction that have no function.

Manufacturing tolerances for width and spacing

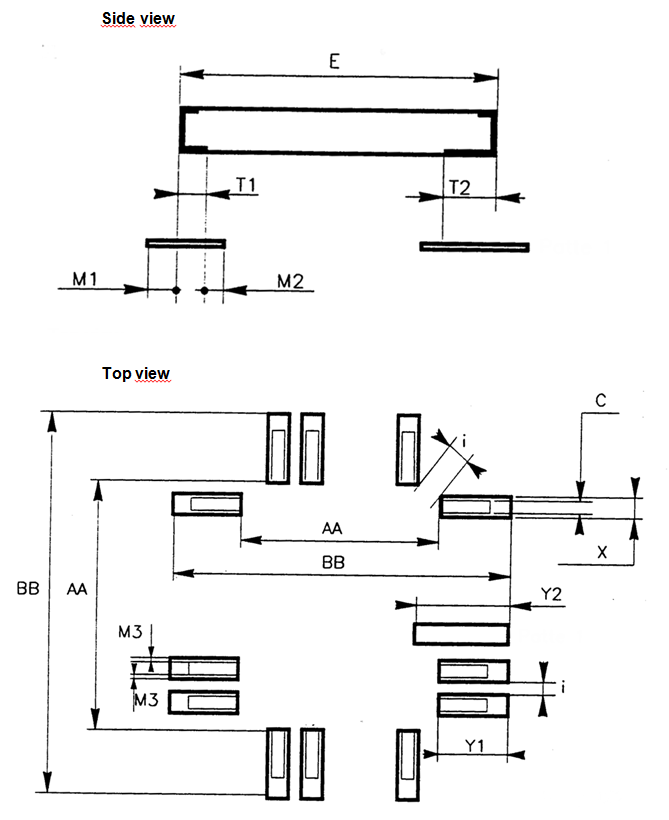

The relative manufacturing tolerances on the track width and spacing of internal and external layers shall be as specified in Table 73.

The maximum absolute manufacturing tolerances on the track width and spacing of internal and external layers shall be as specified in Table 73.

- 1 For example, an internal track width of 400 µm on 35 µm copper thickness has a relative tolerance of ± 20 %, i.e. 80 µm, which is limited by the maximum absolute tolerance of 50 µm.

- 2 The tolerance applies to as-designed dimensions. For example, a spacing as-designed of 200 µm with a tolerance of ± 20 % results in a spacing as-manufactured of 160 µm - 240 µm. Typically, the minimum spacing of 160 µm is important for PCB design.

The use of planarization, copper reduction or surface preparation processes shall be excluded in the definition of the total copper thickness. - 1 Plating of sequential half stacks can be done with different plating methods, like panel plating, selective pattern plating or a combination and can include copper surface reduction processes to reduce copper surface thickness and give best options for fine pitch etching.

- 2 The plated copper thickness as-designed is 25 µm. This can be a thicker layer as-manufactured.

Table 73: Tolerance on track width and spacing of internal and external layers

|

Thickness category [µm]

|

Basic Cu

|

Plated Cu

|

Total Cu thickness

|

Relative tolerance on track width and spacing

|

Maximum absolute tolerance on track width and spacing

|

|

Th17

|

≤ 17

|

0

|

≤ 17

|

± 20 %

|

± 30 µm

|

|

17<Th60

|

≤ 17

|

1x25

|

≤ 42

|

± 20 %

|

± 50 µm

|

|

35

|

0

|

35

| |||

|

35

|

1x25

|

60

| |||

|

60<Th70

|

≤ 17

|

2x25

|

≤ 67

|

± 50 µm

| |

|

70

|

0

|

70

| |||

|

70<Th95

|

35

|

2x25

|

85

|

± 70 µm

| |

|

70

|

1x25

|

95

| |||

|

Note: Explanation of "FOR" is given in Table 131.

| |||||

External layers

The as-manufactured track width and spacing as a function of copper thickness for external layers of rigid PCB shall be in conformance with the values specified in the Table 74.

The as-designed track width and spacing for external layers of rigid PCB should be in conformance with the values specified in the Table 137 except the case specified in the requirement 7.4.3c.

In case the as-designed track width and spacing for external layers of rigid PCB is less than the values specified in the requirement 7.4.3b, the following conditions shall be met:

- the manufacturing tolerances as specified in the PID are smaller than as specified in Table 73,

- the as-manufactured dimensions specified in Table 74 and Table 137 are met, and

- it is recorded as a Review Item in the PCB definition dossier.

Tracks should not be routed on external layers.

In case tracks are routed on external layers they should not be routed under components.

The basic copper foil thickness of fine pitch shall be 17 µm.

Fine pitch track width and spacing may be used in case: - fine pitch tracks are used to route to the footprint of a fine pitch component,

- the length of fine pitch tracks is ≤ 20 mm from the solder pad,

- conformal coating is applied on fine pitch tracks or pads in conformance with the requirement 13.8.4b,

- the voltage is ≤ 30V, and

- it is recorded as a Review Item in the PCB definition dossier.

A long fine pitch track can cause solder pearls.

Spacing and width of pads shall be in conformance with the requirements for tracks specified in 7.4.3a, 7.4.3b, 7.4.3c, 7.4.3f and 7.4.3g.

Table 74: Minimum as-manufactured track width and spacing for external layers as a function of copper thickness

|

Basic Cu

|

Plated Cu

|

Thickness category [µm]

|

Pitch

|

As-manufactured

| |

|

width [µm]

|

spacing [µm]

| ||||

|

17

|

1x 25

|

17<Th60

|

fine/normal

|

120/160

|

120/160

|

|

17

|

2x 25

|

60<Th70

|

fine/normal

|

120/160

|

120/160

|

|

35

|

1x25

|

17<Th60

|

normal

|

160

|

160

|

|

35

|

2x25

|

70<Th95

|

normal

|

240

|

240

|

|

70

|

1x25

|

70<Th95

|

normal

|

240

|

240

|

Normal pitch tracks on internal layers

The as-manufactured track width and spacing as a function of copper thickness for internal layers of rigid PCB shall be in conformance with the values specified in the Table 75.

The as-designed track width and spacing for internal layers of rigid PCB should be in conformance with the values specified in the Table 137 except the case specified in the requirement 7.4.4c.

In case the as-designed track width and spacing for internal layers of rigid PCB is less than the values specified in the requirement 7.4.4b, the following conditions shall be met:

- the manufacturing tolerances as specified in the PID are smaller than as specified in Table 73,

- the as-manufactured dimensions specified in Table 75 and Table 137 are met, and

- it is recorded as a Review Item in the PCB definition dossier.

The thickness category of copper on internal layers shall be as specified in Table 73.

Table 75: Minimum as-manufactured track width and spacing for internal layers as a function of copper thickness

|

Thickness category[µm]

|

Pitch

|

As-manufactured

| |

|

width [µm]

|

spacing [µm]

| ||

|

Th17

|

fine/normal

|

80/104

|

96/104

|

|

17<Th60

|

normal

|

120

|

120

|

|

60<Th70

|

normal

|

160

|

160

|

|

70<Th95

|

normal

|

240

|

240

|

Fine pitch tracks on internal layers

Except the case specified in the requirement 11.5.5a, the track width and spacing for fine pitch on internal layers shall be in conformance with the as-manufactured dimensions specified in Table 75.

Requirement 11.5.5a specifies track width and spacing for impedance controlled routing to AAD with 1 mm pitch on HDI PCBs .

In case fine pitch tracks are used, this shall be recorded as a Review Item in the PCB definition dossier.

Fine pitch shall be limited to the functionality of impedance control or signal routing to AAD.

Fine pitch tracks shall be limited to ≤ 30 V.

For routing to AAD, fine pitch tracks shall fan out to normal pitch as soon as they are outside the AAD footprint.

In case no other circuitry is adjacent that requires the use of fine pitch, the routing of fine pitch tracks shall increase the insulation distance and track width as specified for normal pitch in the Table 75.

- 1 CAD software can implement different minimum insulation distances and track widths in areas with different space available.

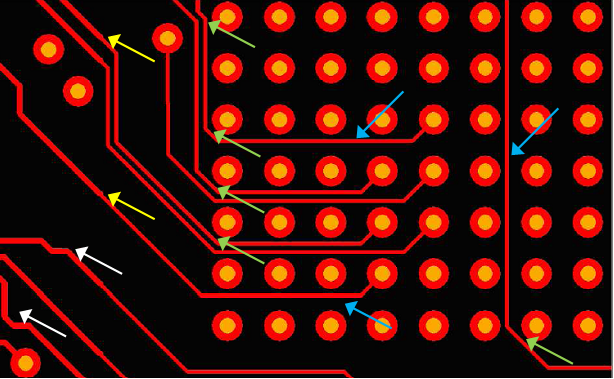

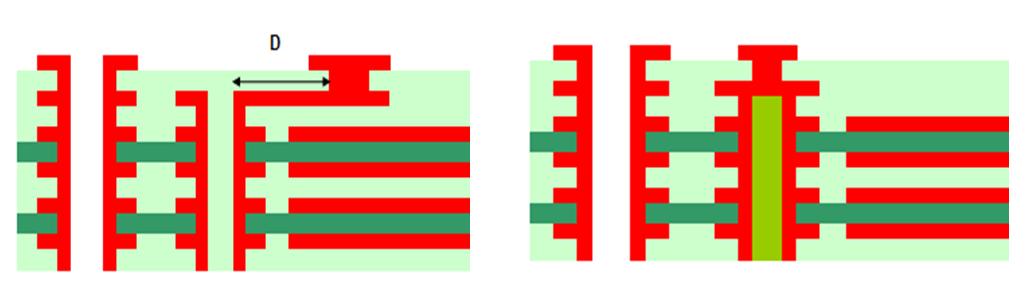

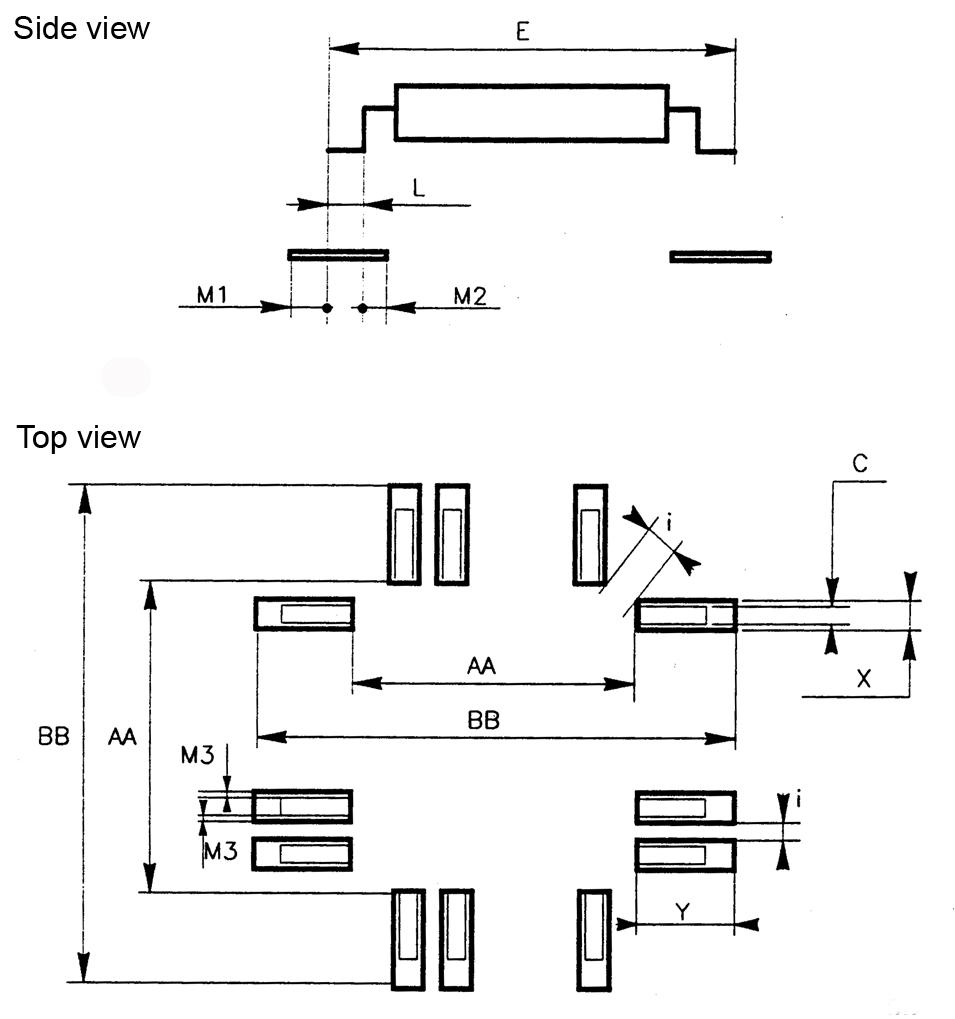

- 2 The Figure 71 shows examples of possible improvements in routing.

Fine pitch shall be manufactured by using 17 µm basic copper thickness without plating steps.

Routing to AAD footprint on internal layers

Tracks in AAD footprint shall be placed equidistant between pads to increase insulation distance to both pads.

See example of nonconformance indicated by blue arrow in Figure 71.

Tracks shall exit from AAD footprint before changing direction to keep the insulation distance to the pad in compliance with normal pitch as specified in Table 75.

See example of nonconformance indicated by green arrow in Figure 71.

Widening of tracks shall occur close to AAD footprint to provide a wider track where no other circuitry is adjacent that requires the use of fine pitch.

See example of nonconformance indicated by yellow arrow in Figure 71.

Changing of direction of track should be in compliance with the requirement 7.4.1a.

See example of nonconformance indicated by white arrow in Figure 71

Pads of AAD footprint may be designed with teardrop reinforcement

Pads in Figure 71 are not designed with teardrop reinforcement.

Figure 71: Example of automated fine pitch routing and possible improvements

Figure 71: Example of automated fine pitch routing and possible improvements

Pad design

Non-functional pad removal

Non-functional pads shall be present on all layers, except two cases specified in the requirement 7.5.1b.

The presence of non-functional pads reduce the risk of hole wall pull-away and reduce the risk of cracks in resin-rich areas.

Non-functional pads may be removed:

- when the presence of the pads degrade the electrical performance, they can be removed by the supplier, or

- to prevent high pressure area during lamination that cause resin starvation in the prepreg, the pads can be removed by the PCB manufacturer.

Removal of non-functional pads is approved by supplier and PCB manufacturer during MRR in conformance with the requirement 7.5.1c.6

When non-functional pads are removed as specified in the requirement 7.5.1b, the following conditions shall be met:

- non-functional pads are present on all copper plane layers,

- non-functional pads are present on flex laminate,

- maximum half of the non-functional pads in the pad stack are removed,

- non-functional pads are removed on maximum two consecutive layers,

- non-functional pads are removed on maximum one side of a laminate, and

- it is recorded as a Review Item in the PCB definition dossier. Non-functional pads should not be removed on layer 2 and n-1.

Pad dimensions

Except the case specified in the requirement 11.5.2a, the annular ring as-manufactured on internal layers shall be in conformance with the requirement 9.5.b.15(d) of ECSS-Q-ST-70-10.

- 1 This requirement specifies 50 µm.

- 2 Requirement 11.5.2a specifies annular ring of internal pads for fine pitch footprint on HDI PCBs.

The annular ring as-manufactured on component side of external layers shall be in conformance with the requirement 9.5.b.15(b) of ECSS-Q-ST-70-10.

This requirement specifies 100 µm.

Except the case specified in the requirement 7.5.3b.2, the annular ring as-manufactured on solder side of external layers shall be in conformance with the requirement 9.5.b.15(a) of ECSS-Q-ST-70-10.

This requirement specifies 200 µm

For component holes on solder side the minimum diameter of external pads should be the diameter of as-manufactured hole plus ≥ 0,8 mm.

For component holes on solder side the minimum diameter of external pads may be the diameter of as-manufactured hole plus ≥ 0,6 mm in case:

- the as-manufactured annular ring as specified in the requirement 7.5.2c,

- the component holes are a footprint for a nano D connector,

- it is recorded as Review Item in the PCB definition dossier.

For via holes and component holes on component side the diameter of external pads should be the diameter of as-manufactured hole plus ≥ 0,6 mm.

For via holes and component holes on component side the diameter of external pads may be the diameter of as-manufactured hole plus ≥ 0,5 mm in case: - the as-manufactured annular ring as specified in the requirement 7.5.2b, and.

- it is recorded as a Review Item in the PCB definition dossier. The diameter of internal pads should be the diameter of drilled hole plus ≥ 0,3 mm.

- 1 The drilled diameter is typically 0,2 mm larger than the as-manufactured minimum hole diameter.

- 2 It is important to consider the number of drilling and lamination sequences and the PCB manufacturing tolerances for the design of the diameter of the pads.

The diameter of pads may be the diameter of the drilled hole plus < 0,3 mm in case this is recorded as a Review Item in the PCB definition dossier.

Tear drop reinforcement of pads to tracks can be used for a more robust design and to mitigate the risk of a smaller designed diameter.

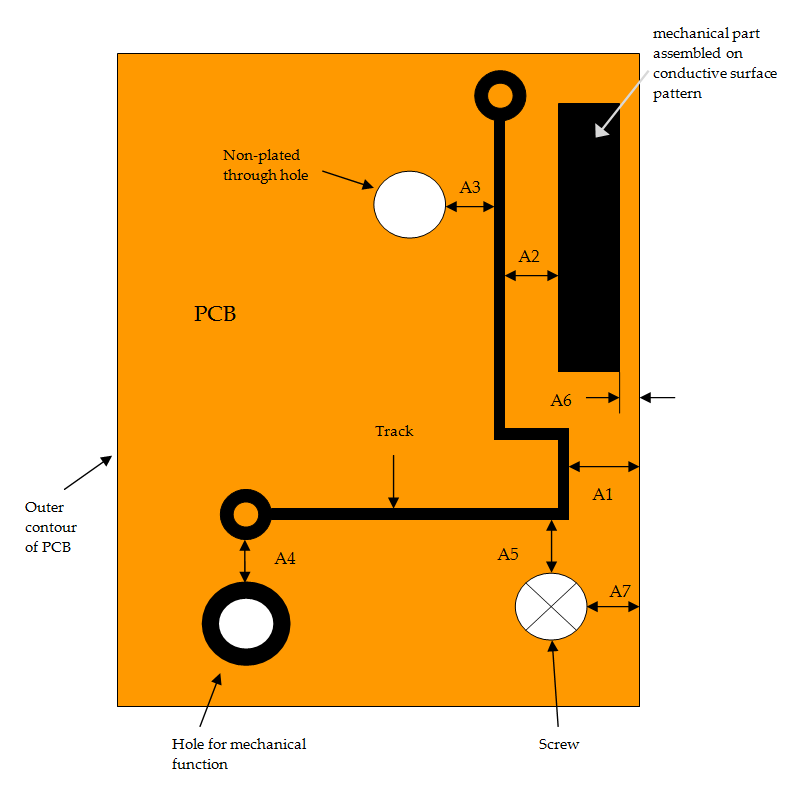

Non-circular external pads

Pads for component holes on external layers shall be circular, except cases specified in the requirement 7.5.3b.

Non-circular pads may be used for component holes, in case the following conditions are met:

- the surface area of the oblong pad is not smaller than the surface area of the circular pad as specified in the requirements from the clause 7.5.2,

- the oblong pad meets the requirement for annular ring of 100 µm as-manufactured, and

- it is recorded as a Review Item in the PCB definition dossier.

- 1 For the requirement 7.5.3b.1 A(oblong) in Figure 72 is the surface area of the oblong pad and A(circular) in Figure 72 is the surface area of a circular pad

- 2 For the requirement 7.5.3b.2 see Annular ring(oblong) in Figure 72

- 3 The design in the requirement 7.5.3b.2 is a deviation of the requirement 7.5.2c (and ECSS-Q-ST-70-10 requirement 9.5b.15.a) of 200 µm annular ring for pads on solder side (see Annular ring(circular) in Figure 72) in one direction, compensated by a larger annular ring in the other direction.

- 4 Other non-circular pad designs are possible and typically used on external layers for AAD and SMT components. Dog-bone shapes or key hole shapes can be used for the verification of solder joint quality or to prevent thermal stress on (blind or micro) vias.

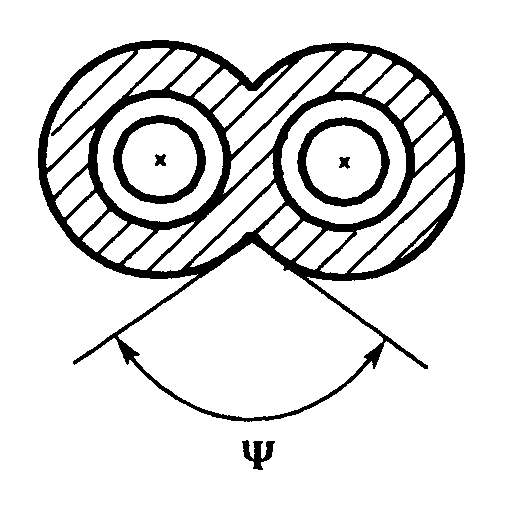

Figure 72: Comparison between circular and oblong pads showing annular ring and the centre of the hole misregistered with the centre of the pad

Figure 72: Comparison between circular and oblong pads showing annular ring and the centre of the hole misregistered with the centre of the pad

Copper planes in rigid PCB

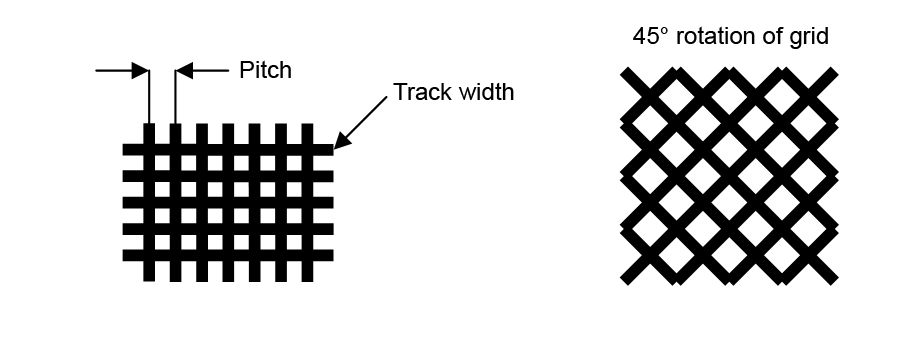

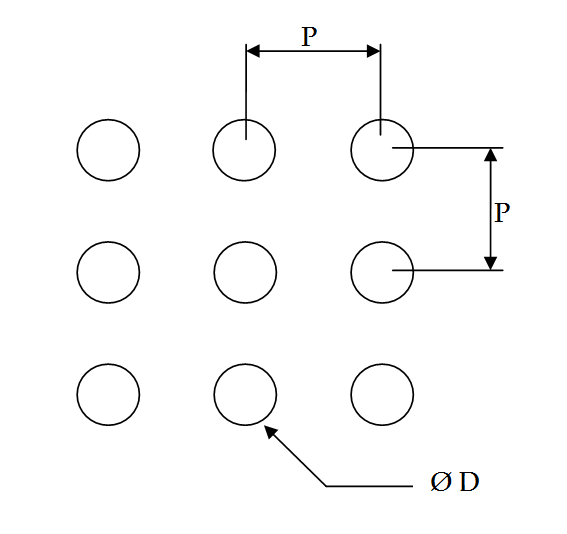

Copper planes should have additional openings in a grid format.

- 1 For example, planes larger than 10 cm2 can be designed using a grid.

- 2 An example of a grid plane is shown in Figure 73.

The grid should be offset between layers.

These additional openings act as venting holes for desorption of humidity out of the PCB. For example, a grid can be 0,4 mm lines at a pitch of 0,6 mm and at 45° angle. The thermal and electrical resistance across such hatch plane is a factor of 2,5 larger than across a solid plane, assuming pattern as specified above. This can affect both power distribution and signal integrity, in particular for RF or digital PCB.

For partial copper planes, balancing of copper should be performed in conformance with requirements 7.1.2d and 7.1.2e.

Copper layers should be placed symmetrically within the build-up.

This is done to limit warp and twist.

In case copper layers are placed asymmetrically within the build-up, this shall be recorded as a Review Item in the PCB definition dossier.

Figure 73: Grid copper plane with openings

Figure 73: Grid copper plane with openings

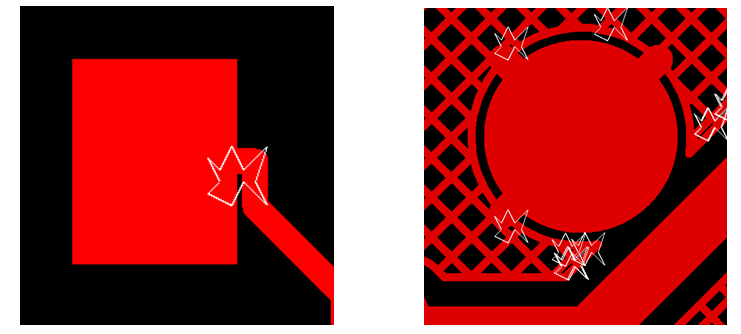

Design considerations for the prevention of sliver and peelable

All areas of the conductive patterns as well as areas of insulating dielectric shall have a dimension of ≥ 0,1 mm in X and Y direction after etch compensation.

This is done to prevent sliver or peelable see Figure 74.

Figure 74: Example of peelable (left) and sliver (right)

Figure 74: Example of peelable (left) and sliver (right)

PCB surface finish

Metallization

Plating of metallic layers and finishes shall be done in conformance with the requirements from the clause 5.2.3 of the ECSS-Q-ST-70-11.

Qualified surface finishes are tin-lead reflowed in hot oil and electrolytic gold. Electrolytic gold can be plated over copper or nickel.

Except cases specified in the requirement 7.8.1d, each finish shall be on separate outer layer nets when a single PCB uses a mixed surface finish of electrolytic gold and fused tin-lead.

Separate outer layer nets with mixed surface finishes shall have insulation distance of > 500 µm.

Mixed surface finish may be used on the same outer layer net in case the following conditions are met:

- a tin-lead overlap on electrolytic gold of ≥ 200 µm is used, and

- the distance of gold plating to a solder pad is ≥ 200 µm.

- 1 Condition specified in the requirement 7.8.1d.1 is to ensure coverage of the plated copper.

- 2 Condition specified in the requirement 7.8.1d.2 is to avoid gold-tin embrittlement in the solder joints.

A PCB with mixed surface finishes shall be recorded as a Review Item in the PCB definition dossier.

Other surface finishes than the ones specified in the requirements from 7.8.1a to 7.8.1d may be used for non-soldering purpose.

Solder mask

Overview

Solder mask has been used traditionally to prevent solder flowing away from AAD in a dog-bone footprint, possibly with through-hole vias. Instead, it is recommended to design with via-in-pad (blind, micro or filled via). Problems seen with solder mask include poor adhesion to tin-lead, poor outgassing performance, high risk associated with selective stripping of tin-lead, the implementation of a width of ≥ 200 µm to ensure adhesion and a transition zone of solder mask overlapping on tin-lead to prevent exposed copper and allow for registration tolerance.

Use of solder mask

Solder mask shall not be used.

Flex PCBs

Overview

This clause specifies requirements for flex PCBs with the purpose to maintain flexibility and achieve mechanical strength.

Dynamic applications

Dynamic applications with flex PCBs shall be project qualified.

The testing of flex PCBs only covers static applications and the integration of the PCB.

PCB build-up

General

The maximum number of copper layers on a flex PCB shall be 2.

Thickness of a flexible PCB shall be ≤ 0,6 mm over the cover layers as-designed and as-manufactured.

This assumes maximum thickness of laminate, copper, adhesive and cover layer.

Dielectric materials

Flex PCBs shall be manufactured with copper clad flexible polyimide laminate without adhesive between copper and laminate.

- 1 This laminate type is named “adhesiveless”.

- 2 The laminate typically used is of type Pyralux AP from DuPont.

The as-designed thickness of the flex laminate shall be 25 µm , 50 µm, 75 µm, 100 µm or 150 µm.

50 µm thickness is preferred.

The tolerance for the as-manufactured thickness of the flex laminate shall be:

- for ≤ 50 µm flex laminate: ≤ ±12,5 %, and

- for ≥ 75 µm flex laminate: ≤ ±10 %.

This implies that for the as-manufactured PCB, the minimum insulation between two layers of flexible laminate in Z direction is 22 µm.

The thickness of the polyimide cover layer shall be 25 µm or 50 µm.

The thickness of the acrylic adhesive on the cover layer shall be 25 µm or 50 µm.

A typical cover layer is of type Pyralux LF from DuPont.

Copper cladding

The thickness of copper cladding shall be 17 µm, 35 µm or 70 µm.

Thickness of copper cladding 70 µm should not be used.

This is recommended to avoid risk in the bonding cycle of the cover layer.

In case copper cladding of 70 µm is used, this shall be recorded as a Review Item in the PCB definition dossier.

Copper cladding on flex laminate of >17 µm shall be the type “rolled and annealed”.

Copper cladding on flex laminate of 17 µm shall be the type “rolled and annealed” or “electrodeposited”.

Copper planes in flex PCB

Full copper planes should not be used except the case specified in the requirement 8.3.4b.

In case full copper planes are used, this shall be recorded as a Review Item in the PCB definition dossier.

In case a copper plane is used in a flex PCB, a grid with openings should be implemented as specified in the Figure 73.

The purpose of the openings is to improve adhesion of the cover layer, desorption of humidity and flexibility of the PCB. A grid can be 0,4 mm lines at a pitch of 0,6 mm and at 45° angle. It is preferable to have the grid offset between layers. In this case, the electrical and thermal resistance increases by a factor of approximately x2,5 compared to a solid plane.

Track design

Tolerances on track width and spacing shall be as specified in the Table 73.

Track width shall be as specified in the Table 75 for normal pitch.

Track width shall be minimum 120 µm as-manufactured.

Spacing shall be as specified in the requirements of the clause 13.8.3.

Tracks should be evenly distributed over the entire width of the PCB.

Non-functional tracks may be used to achieve an even distribution of tracks over the entire width of the PCB.

Tracks on double-sided boards should not be superimposed and a clearance distance in X,Y direction should be implemented.

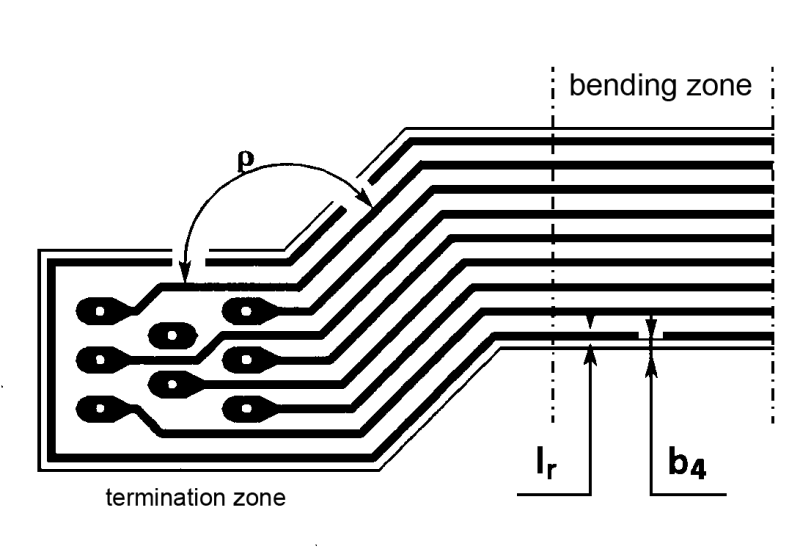

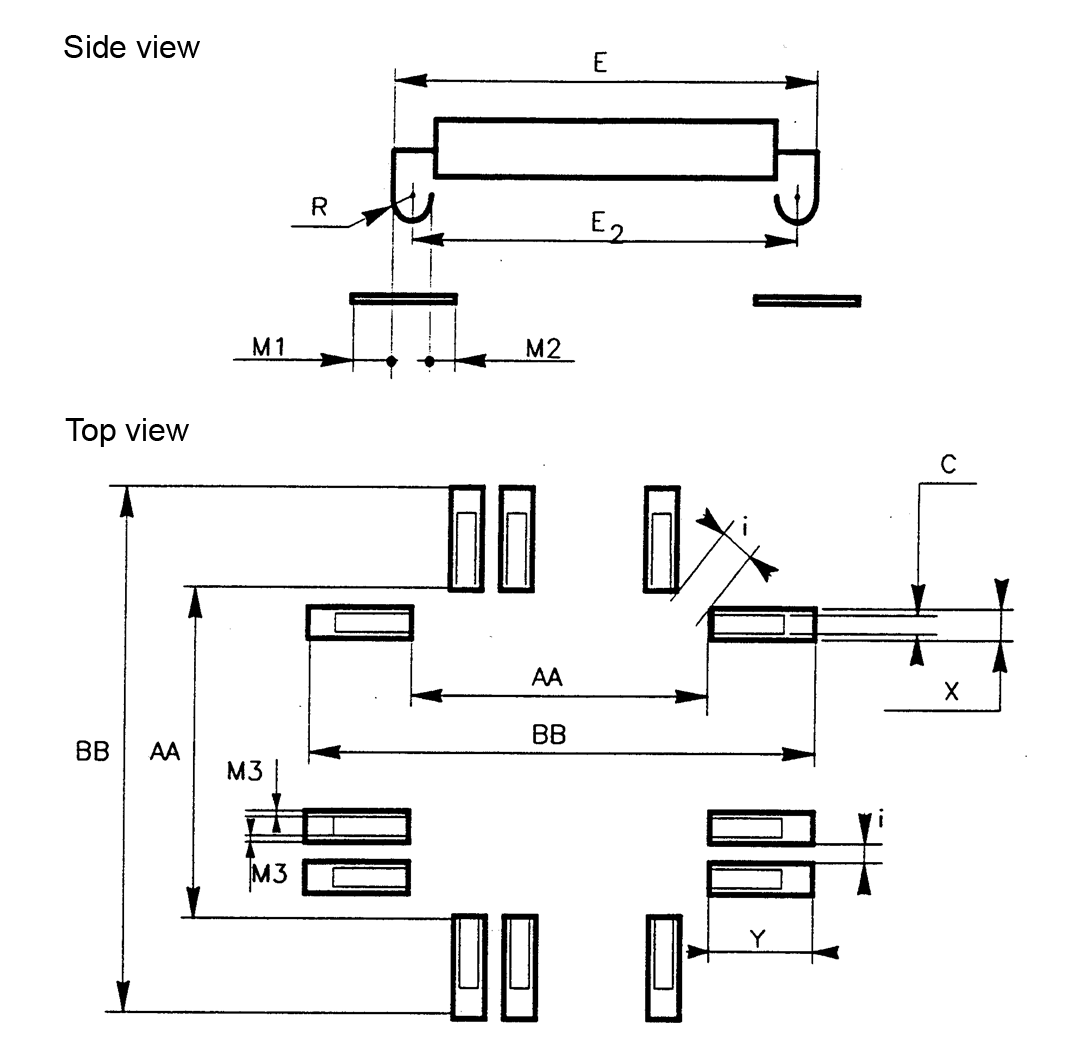

This is done to reduce the local thickness. An example of off-set tracks is shown in Figure 81.

Edges of tracks should not be superimposed.

This is done to prevent localised high pressure during lamination.

Figure 81: Clearance of tracks on flex PCBs.

Figure 81: Clearance of tracks on flex PCBs.

Tracks shall not change direction within the bending zone, as specified in Figure 82.

The edge of the PCB should include on one side of the laminate a non-functional track as mechanical reinforcement with a width of ≥ 0,3 mm.

- 1 This is indicated as “Ir” in Figure 82.

- 2 The non-functional track for mechanical reinforcement is named reinforcement strip.

The reinforcement strip should be implemented on the following areas: - Termination zone when no other mechanical fixing is designed apart from the termination leads,

- Zone where a change of direction of tracks or copper plane occurs,

- Bending zone. The distance of tracks or reinforcement strip to the edge of the board shall be ≥ 0,5 mm.

This is indicated as “b4” in Figure 82.

The distance of tracks or reinforcement strip to the edge of the board should be ≥ 1,0 mm.

Track width and spacing shall be in conformance with the values specified in the Table 134.

When tracks change direction, the angle (p) shall be ≥ 135° as specified in the Figure 82.

It is recommended to design tracks as straight as possible.

Figure 82: Tracks on flex, defining termination and bending zones.

Figure 82: Tracks on flex, defining termination and bending zones.

Through holes

Annular ring

Annular ring on a flex PCB shall be the distance of the surface copper from the hole wall to the clearance opening in the cover layer.

Adhesive protruding from underneath the cover layer onto the surface copper shall be subtracted from the annular ring measurement.

Annular ring as-manufactured on a component hole shall be ≥ 0,25 mm.

Annular ring as-manufactured on non-soldering hole shall be ≥ 0,1 mm.

Vias and pads

PTH shall be located only in termination zones, not in the bending zone, as specified in Figure 82.

Terminal pads shall include PTH.

Terminal pads on single sided board have risk to be damaged during assembly. Terminal pads need to be reinforced by plating.

The cover layer shall include a clearance for assembly of a PTH in conformance with the clause 8.5.1.

Tear drop pad for flex PCB

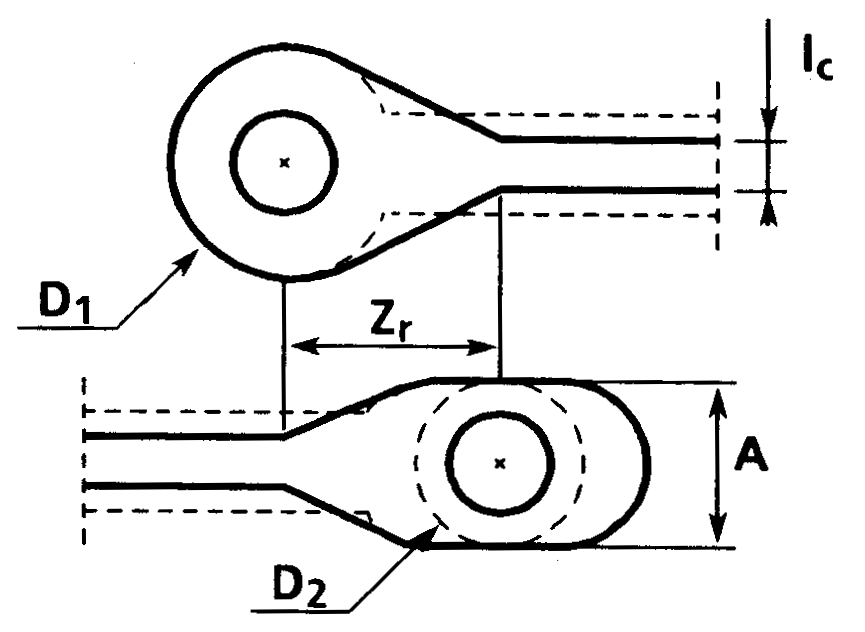

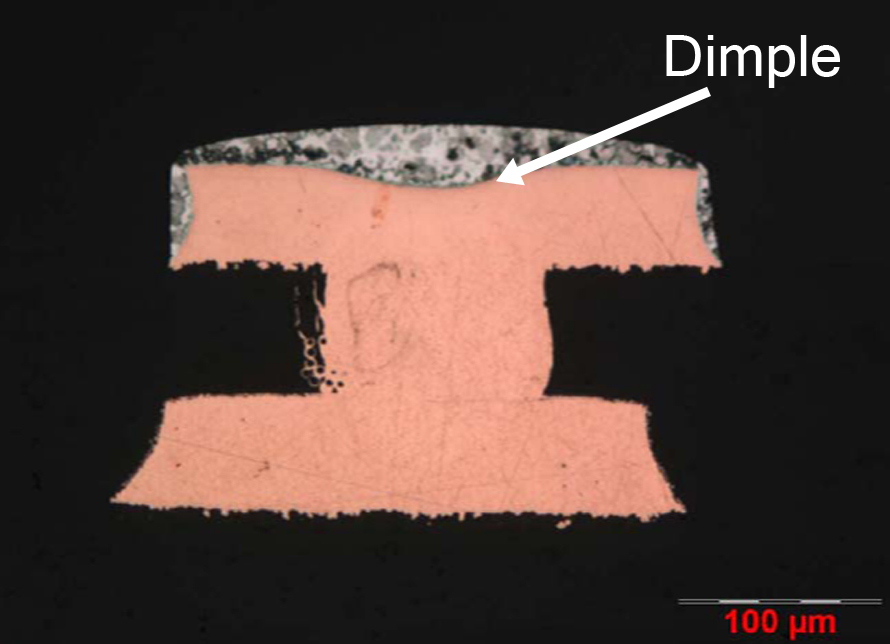

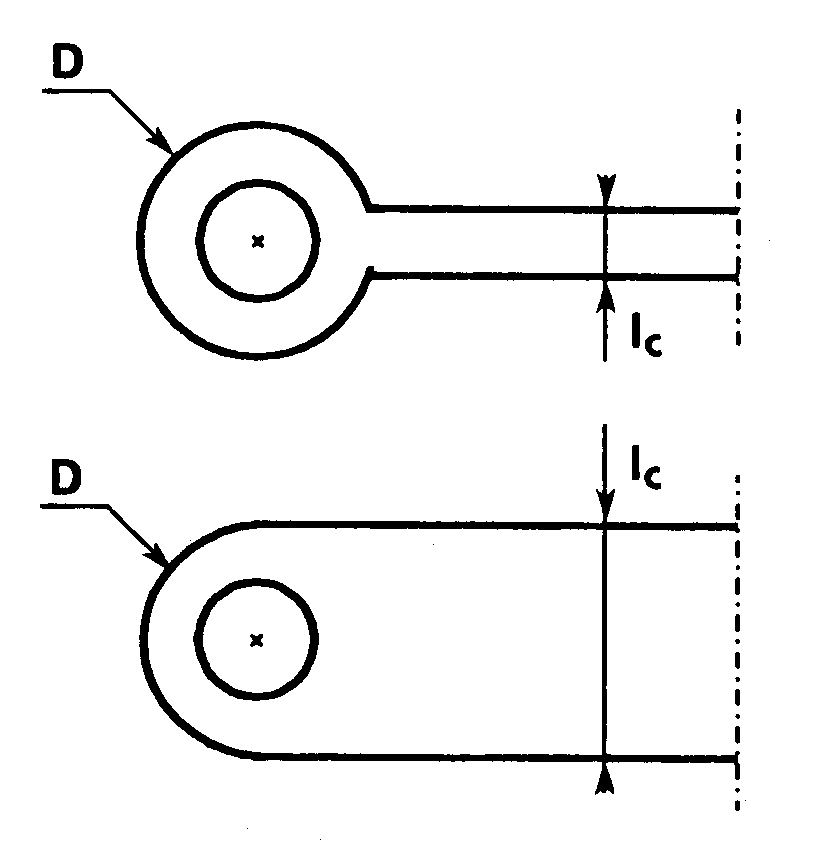

The diameter of a circular pad with or without teardrop reinforcement shall be D1 as specified in Figure 83.

The diameter of an oblong pad shall be equal to D2 as specified in Figure 83.

The track width should be at least half the diameter of the pad except the case specified in the requirement 8.5.3d.

In the Figure 83 IC is track width and D1, D2 are diameters of the pad.

The track width may be less than half of the diameter of the pad in case the following conditions are met:

- a teardrop reinforcement is added to the connection of the track to the pad, and

- the reinforced zone has a length ≥ 0,8x the diameter of the pad.

In Figure 83 Zr is the length of the reinforced zone.

Figure 83: Teardrop reinforcement of terminal pads in flex PCB.

Figure 83: Teardrop reinforcement of terminal pads in flex PCB.

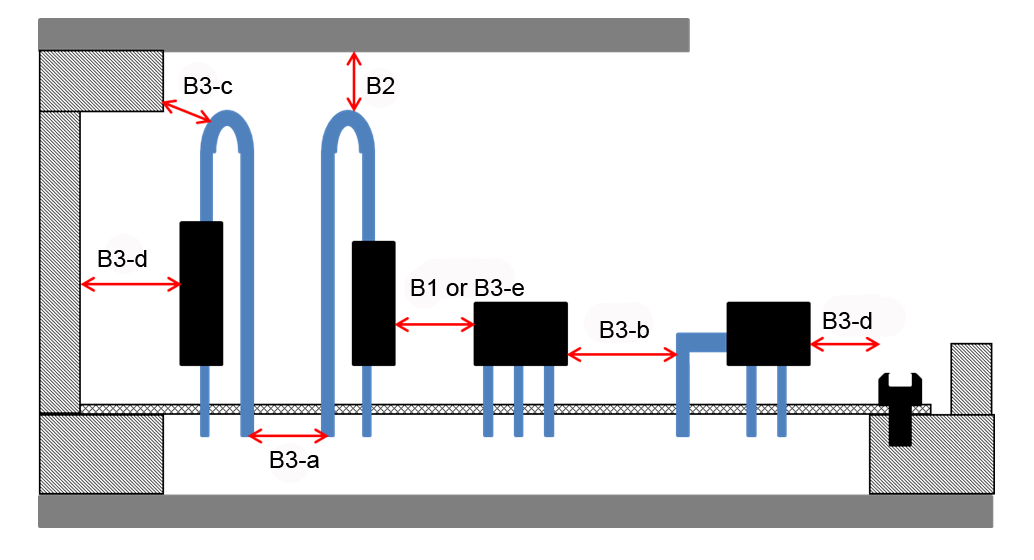

Bending radius

Overview

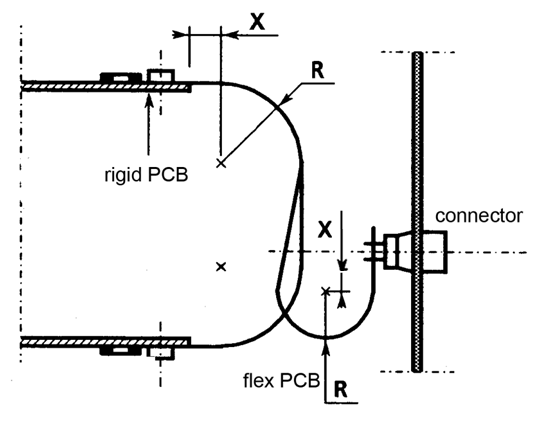

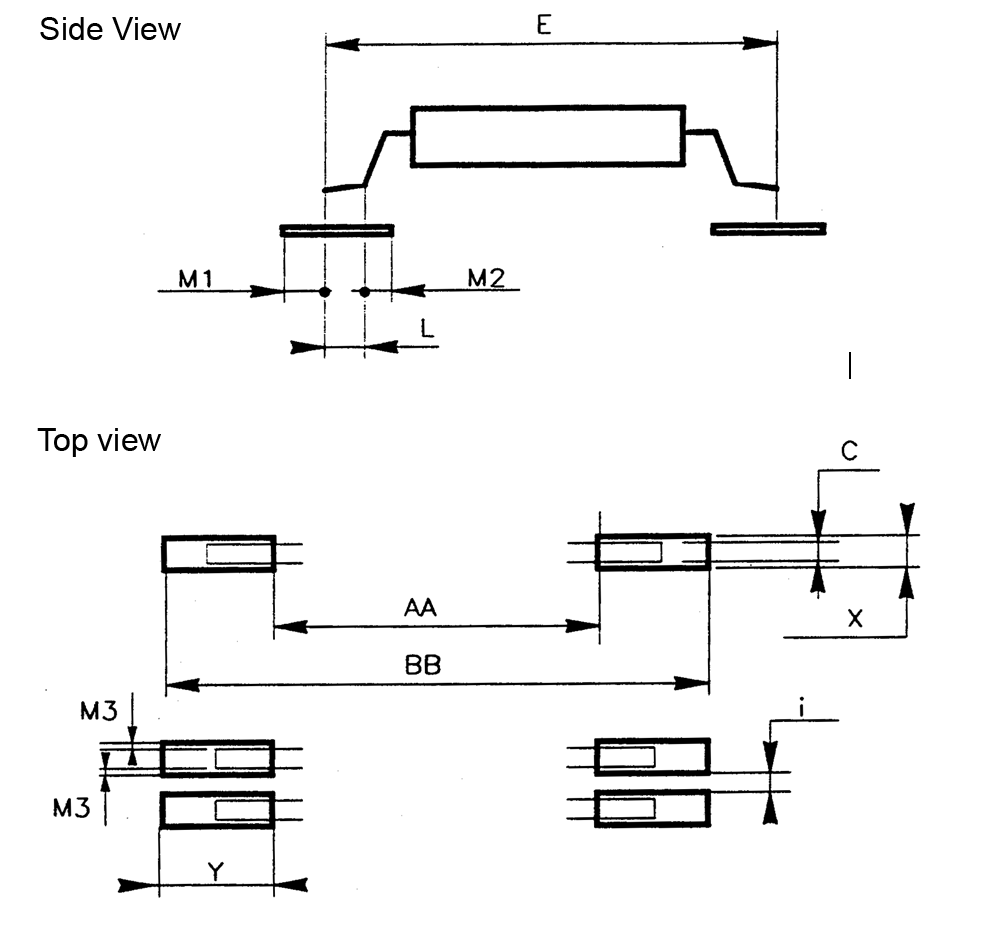

The PCB is designed to bend in L, U or S shapes with a radius of flexion that enables the PCB to be mounted and dismounted without damage. These radii depend on the type of board, the thickness of laminate and copper layers and a static or dynamic bending application, see Figure 84.

General

The radius on a flex PCB having 50 µm laminate thickness and 35 µm double sided copper thickness and including cover layer shall be ≥ 12x total thickness of the flex for a static application.

In the Figure 84 R is the bending radius of a flex PCB

Other PCB build-ups or dynamic applications shall be qualified by the supplier.

Other PCB build-ups include thicker laminate, thicker copper, or multilayers

The termination zone shall include all termination pads.

Bending of the flex PCB shall be designed not to occur on the termination zone and on an additional distance of 2 mm.

- 1 In the Figure 84 the additional distance is indicated as X.

- 2 Even though no bending is designed to occur on the termination zone, some bending can still occur on the assembled PCB due to the stress on the flex section. A stiffening of the termination zone by implementing double cover layer or adhesive can decrease the bending locally.

Figure 84: Bending radius of assembled flex

Figure 84: Bending radius of assembled flex

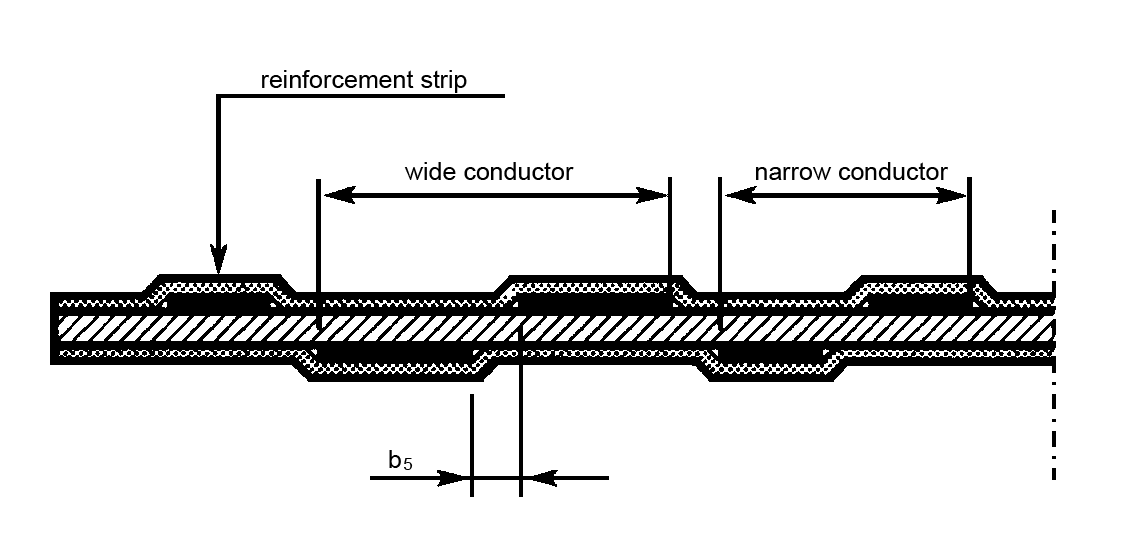

Sculptured flex PCB

Overview

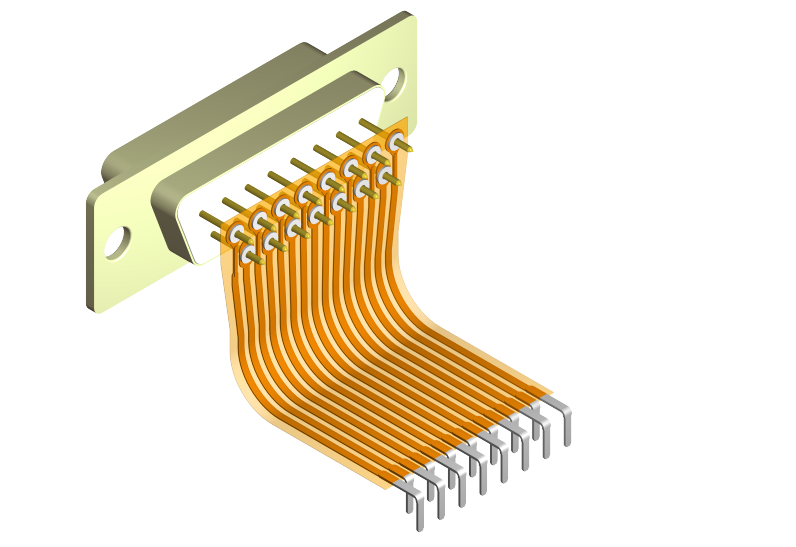

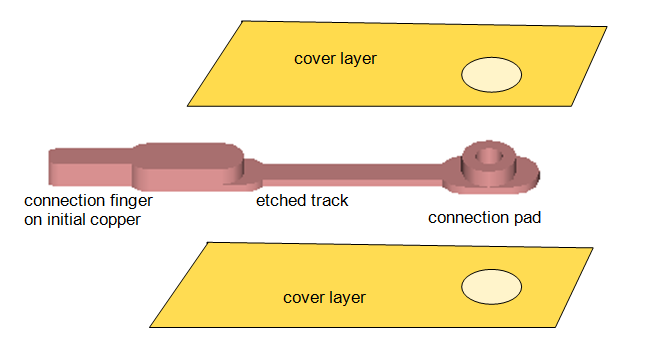

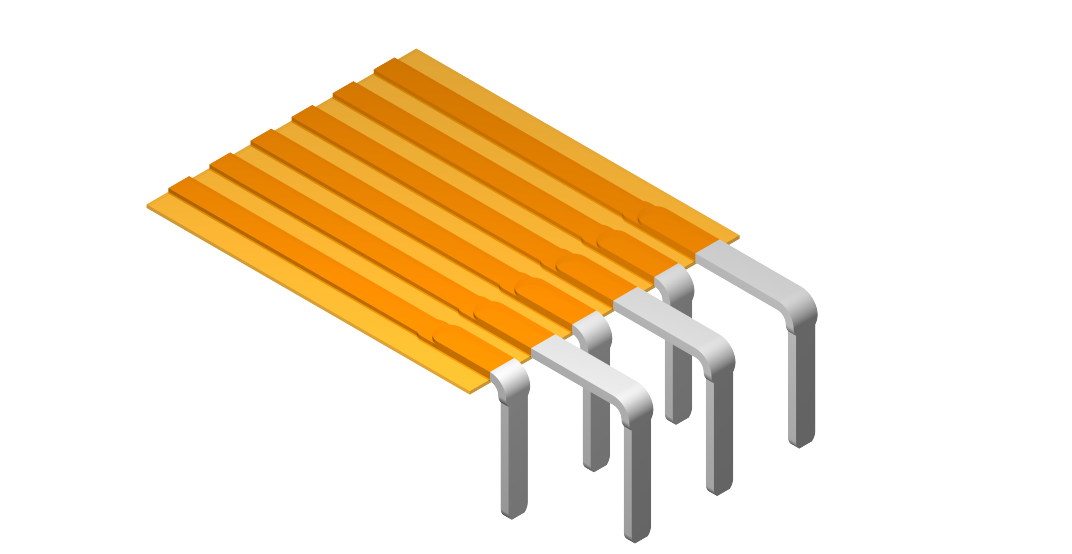

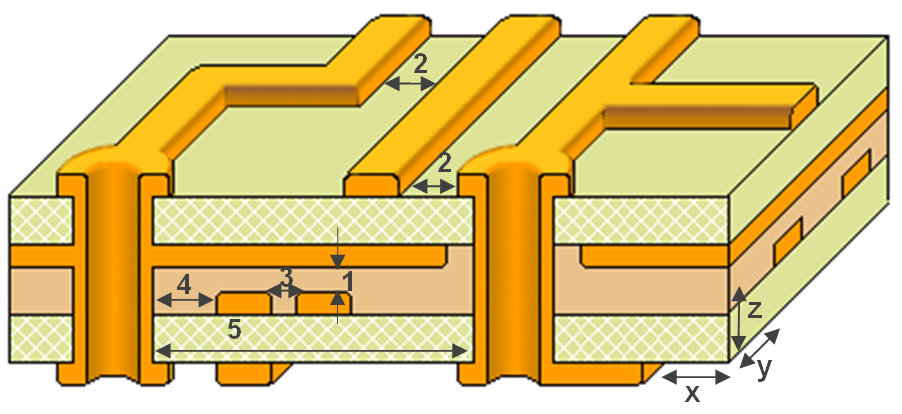

Sculptured flex PCBs can be used as a connection between 2 PCBs or connectors. Sculptured flex circuits comprises of a copper circuit with different thickness sandwiched between two cover layers, as illustrated in Figure 85 and Figure 86.

General

The thickness of the cover layer, excluding adhesive, shall be 25 µm.

The thickness of the acrylic adhesive of the cover layer shall be 50 µm or 75 µm.

A typical cover layer is type Pyralux LF 0210 from DuPont.

The surface finish shall be in conformance with the requirement 7.8.1b.

- 1 This requirement specifies the use of hot oil reflowed tin-lead.

- 2 The connector pins are cut after reflow and exposed copper is permitted.

Figure 85: Sculptured flex circuit

Figure 85: Sculptured flex circuit

Copper foil dimensions for build-up

A single foil of copper shall be used in the build-up.

Copper clad laminate is not used.

The initial thickness of the copper foil shall be 250 µm or 300 µm.

Copper type CW004 grade R240 ( ½ hard )

The sculptured shape of the copper shall be manufactured by selective etching of the copper foil.

The build-up, initial and etched copper thickness, track width and insulation distance shall be in conformance with the minimum dimensions specified in Table 81.

Table 81: Minimum as-manufactured dimensions of sculptured flex conductor

|

|

Thick initial copper

|

Thin initial copper

| ||

|

initial copper

|

etched copper

|

initial copper

|

etched copper

| |

|

Initial copper thickness

|

300 µm

|

|

250 µm

|

|

|

Track width for initial copper

|

400 µm

|

300 µm

| ||

|

Insulation distance for initial copper

|

500 µm

|

400 µm

| ||

|

Connection finger width

|

500 µm

|

350 µm

| ||

|

Etched thickness

|

|

150 µm

|

|

100 µm

|

|

Track width for etched copper

|

300 µm

|

200 µm

| ||

|

Insulation distance for etched copper

|

350 µm

|

250 µm

| ||

Figure 86: Build-up of sculptured flex circuit

Figure 86: Build-up of sculptured flex circuit

Connection finger

The connection fingers may be bend in a staggered pattern to fit the footprint of the connecting PCB

An example of staggered bend connection fingers is shown in Figure 87.

Figure 87: Connection finger of sculptured flex circuit

Figure 87: Connection finger of sculptured flex circuit

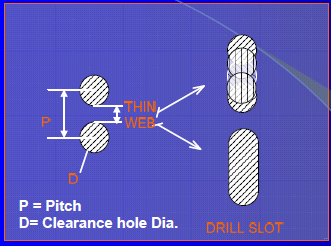

Through-holes

Through-holes shall be manufactured by drilling into the initial copper thickness.

Oblong pads should be used only in case circular pads cannot be used due to insufficient spacing in one direction.

The drill diameter of the hole shall be ≥ 0,5 mm.

Component holes with circular pads should have a pad diameter as-designed of ≥ 0,4 mm larger than the drilled diameter.

This results in a pad size of 200 µm as-designed.

The minimum as-manufactured pad size on the component side may be 0.

The pad size is similar to annular ring but this term is not used for sculptured flex technology. The as-manufactured pad size with misregistration is indicated with the red arrow in Figure 88.

There shall be no adhesive inside the hole.

Adhesive can be squeezed from underneath the cover layer and misregistration of the cover layer on component side can risk to have adhesive inside the hole.

The minimum as-designed pad diameter on the solder side should be ≥ 0,7 mm larger than the drilled diameter.

The annular ring on solder side shall be in compliance with the requirement 7.5.2c.

- 1 Requirement 7.5.2c specifies 200 µm.

- 2 The pad diameter on solder side is indicated with the blue arrow in Figure 88.

Figure 88 Side view of a component hole for sculptured flex

Bending radius

The bending radius of sculptured flex circuit shall be ≥ 12x thickness and ≥ 3,2 mm.

Bending shall only occur on the etched track.

Bending shall not occur on the full thickness copper.

The etched track is shown in Figure 86 and copper thickness is specified in Table 81.

Rigid-flex PCBs

Overview

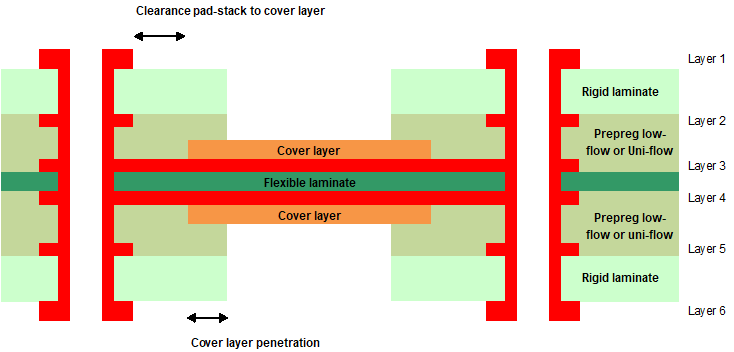

Multiple flex laminates with cover layers can be incorporated within a PCB. Figure 91 shows an example of 1 flex laminate incorporated in the rigid-flex PCB.

Figure 91 Example of a build-up of a 6 layer symmetric rigid-flex

Figure 91 Example of a build-up of a 6 layer symmetric rigid-flex

General

The design of rigid parts of a rigid-flex PCBs shall be performed in conformance with the requirements from the clause 7.

The design of flex parts of a rigid-flex PCBs shall be performed in conformance with the requirements from the clause 8.

Design of rigid and flex parts include track width and spacing.

No termination zone shall be defined for the flex section of a rigid-flex PCB.

Build-up

The symmetry of the build-up shall be in conformance with the requirement 7.1.1a and 7.1.1b.

In the rigid part of the PCB the flex layers shall be bonded by using prepreg.

In the rigid part of the PCB adhesive shall not be used for bonding of the flex layers.

There are different manufacturing principles that either use standard flow prepreg as used in rigid boards, or modified no-flow type prepregs. No-flow prepreg cannot be used for resin filling of blind vias, and thereby a mix of prepreg styles can be necessary, when a sequential rigid-flex board is designed.

Copper foil thickness of 70 µm shall not be used on flex or rigid layers bonded with no-flow prepreg unless it is recorded as a Review Item in the PCB definition dossier.

This can add risk for bonding in cover layer bond cycles or the bond cycle with no-flow prepreg.

The number of flex laminates shall be ≤ 6, which can result in 12 copper layers when double sided flex laminates are used.

Flex layers can be bonded together by using a bondply cover layer with adhesive on both sides. The advantage of this is improved cleanliness between layers and improved control of impedance. The disadvantage is the flexibility and bending radius of the flex stack.

Three flex laminates or more in the build-up shall be recorded as Review Item in the PCB definition dossier.

Three flex laminates can include 6 copper layers.

Except the cases specified in the requirement 9.3h the rigid-flex PCB shall be designed and delivered with a support frame.

The rigid-flex PCB may be delivered without a support frame in case the following conditions are met:

- the PCB manufacturer delivers the rigid-flex PCB with a support that prevents damage to the PCB during shipment, and

- the customer implements a support structure that prevents damage to the rigid-flex PCB during assembly and handling.

Cover layer

The cover layer shall be placed in the flexible section of the PCB.

The cover layer shall not be placed in the rigid section of the PCB, except for the interface to the flex section as specified in the requirement 9.4c.

The cover layer shall extend into the rigid section of the PCB by ≥ 1,5 mm.

In a multilayer rigid-flex PCB where flex laminates are bonded together with bondply, the ends of the cover layers and bondply should be off-set in the rigid section by 1 mm to prevent a line of weakness.

The cover layer shall not overlap the internal pad of a via in the rigid section.

This is done to reduce stress on the hole wall due to high Z-expansion of cover layer adhesive and to maintain a good hole quality by not using dissimilar materials.

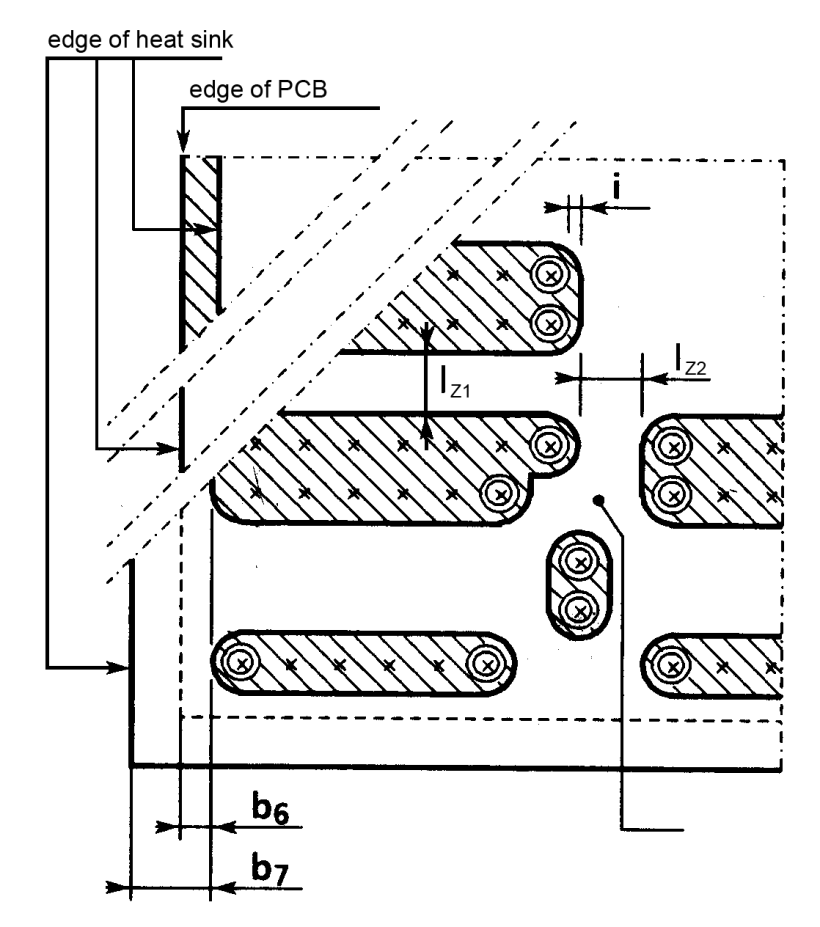

Interface of rigid part and flexible part

The hole wall shall be ≥ 2 mm separated from the edge of the rigid part of the PCB.

A larger separation between hole wall and edge of the rigid part is recommended in case it fits within the PCB lay-out.

Tracks on flex layers shall not change direction within 1 mm on both sides of the interface between flex and rigid sections.

Tracks extend 1 mm out of the rigid part of the PCB before they change direction. Tracks extend 1 mm into the rigid part of the PCB before they change direction.

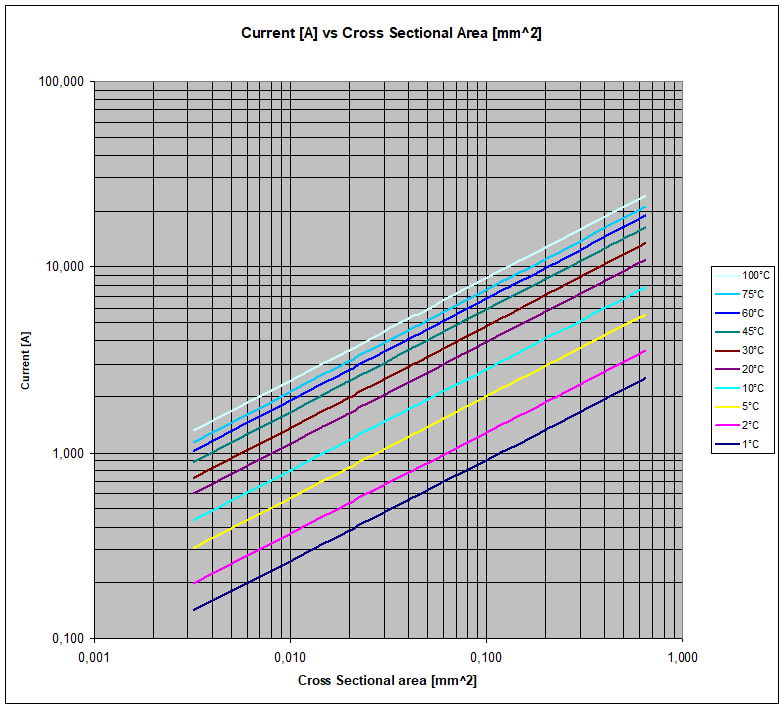

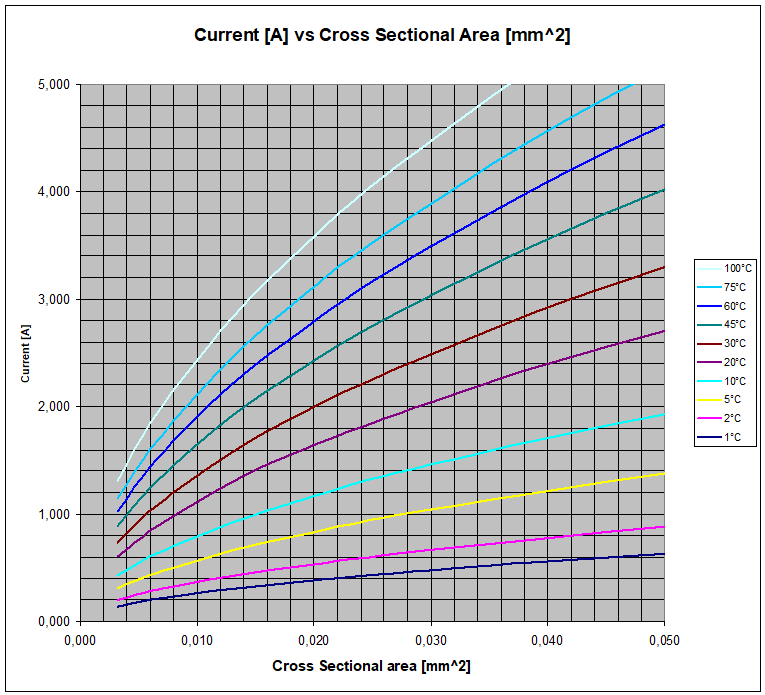

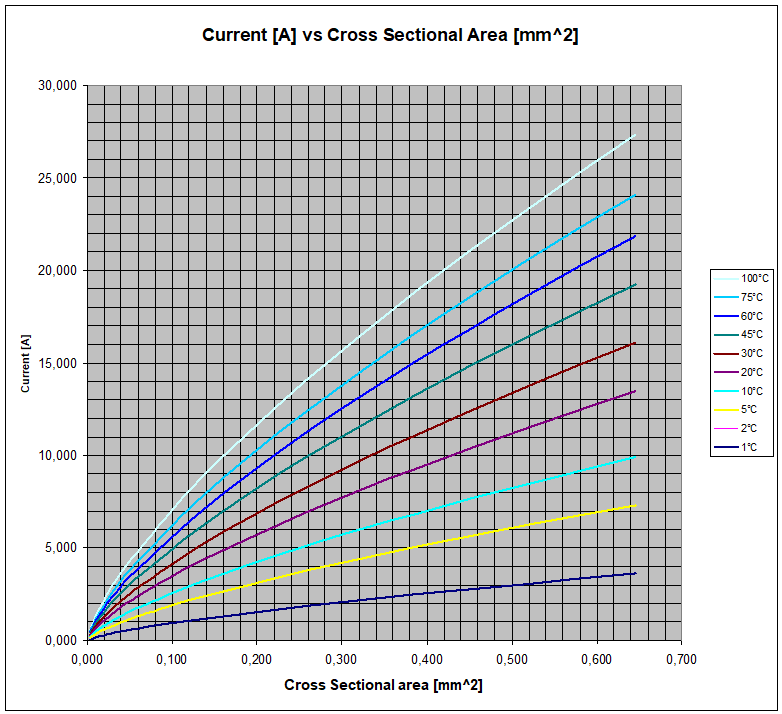

Bending of the flex section shall be performed in conformance with the requirements from the clause 8.6.