Space product assurance

Procurement of printed circuit boards

Foreword

This Standard is one of the series of ECSS Standards intended to be applied together for the management, engineering and product assurance in space projects and applications. ECSS is a cooperative effort of the European Space Agency, national space agencies and European industry associations for the purpose of developing and maintaining common standards. Requirements in this Standard are defined in terms of what shall be accomplished, rather than in terms of how to organize and perform the necessary work. This allows existing organizational structures and methods to be applied where they are effective, and for the structures and methods to evolve as necessary without rewriting the standards.

This Standard has been prepared by the ECSS Executive Secretariat, endorsed by the Document and Discipline Focal Points, and approved by the ECSS Technical Authority.

Disclaimer

ECSS does not provide any warranty whatsoever, whether expressed, implied, or statutory, including, but not limited to, any warranty of merchantability or fitness for a particular purpose or any warranty that the contents of the item are error-free. In no respect shall ECSS incur any liability for any damages, including, but not limited to, direct, indirect, special, or consequential damages arising out of, resulting from, or in any way connected to the use of this Standard, whether or not based upon warranty, business agreement, tort, or otherwise; whether or not injury was sustained by persons or property or otherwise; and whether or not loss was sustained from, or arose out of, the results of, the item, or any services that may be provided by ECSS.

Published by: ESA Requirements and Standards Division

ESTEC, P.O. Box 299,

2200 AG Noordwijk

The

Copyright: 2008 © by the European Space Agency for the members of ECSS

Change log

|

ECSS-Q-70-11A

|

First issue

|

|

ECSS-Q-70-11B

|

Never issued

|

|

ECSS-Q-ST-70-11C

|

Second issue

|

Scope

This Standard defines the requirements imposed on the customer, the supplier and the qualified PCB manufacturer for PCB procurement.

The requirements of clause 7 apply to both qualification and procurement of finished PCBs and do not include the manufacturing tolerances.

This Standard is applicable for the following type of boards:

Rigid PCBs (singlesided, doublesided, multilayer, sequential multilayer and PCBs with metal core)

Flexible PCBs (singlesided and doublesided)

Rigidflex PCBs (multilayer and sequential multilayer)

High frequency PCBs

Special PCBs.

PCBs are used for the mounting of components in order to produce PCB assemblies performing complex electrical functions. The PCBs are subjected to thermo-mechanical stresses during their assembly such as mounting of components by soldering, rework and repair under normal terrestrial conditions. In addition the assembled PCB is subjected to the environment imposed by launch and space flights. Therefore the qualification of a PCB supplier to ECSS-Q-ST-70-10 is of extreme importance before the procurement of PCB for space usage.

This standard may be tailored for the specific characteristics and constraints of a space project in conformance with ECSS-S-ST-00.

Normative references

The following normative documents contain provisions which, through reference in this text, constitute provisions of this ECSS Standard. For dated references, subsequent amendments to, or revision of any of these publications do not apply. However, parties to agreements based on this ECSS Standard are encouraged to investigate the possibility of applying the more recent editions of the normative documents indicated below. For undated references, the latest edition of the publication referred to applies.

|

ECSS-S-ST-00-01

|

ECSS system — Glossary of terms

|

|

ECSS-Q-ST-70

|

Space product assurance — Material, mechanical parts and processes

|

|

ECSS-Q-ST-70-02

|

Space product assurance — Thermal vacuum outgassing test for the screening of space materials

|

|

ECSS-Q-ST-70-07

|

Space product assurance — Verification and approval of automatic machine wave soldering

|

|

ECSS-Q-ST-70-08

|

Space product assurance — Manual soldering of highreliability electrical connections

|

|

ECSS-Q-ST-70-10

|

Space product assurance — Qualification of printed circuit boards

|

|

ECSS-Q-ST-70-28

|

Space product assurance — Repair and modification of printed circuit board assemblies for space use

|

|

ECSS-Q-ST-70-38

|

Space product assurance — Highreliability soldering for surfacemount and mixed technology printedcircuit boards

|

|

IEC 60249 (1993-05)

|

Base materials for printed circuits

|

|

IEC 60326-2-am 1 (1992-06)

|

Printed boards. Part 2: Test methods

|

|

IPC-4101

|

Specification for base materials for rigid and mulitlayer printed boards

|

|

IPC-MF-150F

|

Metal foil for printed wiring applications

|

|

IPC-CF-152B

|

Composite metallic material specification for printed wiring board

|

Terms, definitions and abbreviated terms

Terms from other standards

For the purpose of this Standard, the terms and definitions from ECSS-S-ST-00-01 apply.

Terms specific to the present standard

associated test coupon

small piece of PCB designated to have a limited specific set of tests performed

The associated test coupon is manufactured as part of a PCB and at the final manufacturing stage it is separated from it. The associated test coupon is thus associated with the PCB, with which it was simultaneously manufactured.

blister

delamination in the form of a localized swelling and separation between any of the layers of a lamination base material, or between base material and conductive foil or protective coating

[IEC 60194 (1999-04)]

cover layer (flexible circuit)

layer of insulating material that is applied covering totally or partially over a conductive pattern on the outer surfaces of a PCB

[IEC 60194 (1999-04)]

crazing

internal condition that occurs in reinforced base material whereby glass fibres are separated from the resin at the weave intersections

- 1 This condition manifests itself in the form of connected white spots or crosses that are below the surface of the base material. It is usually related to mechanically induced stress.

- 2 See also “measling”.

[IEC 60194 (1999-04)]

delamination

separation between plies within a base material, between base material and a conductive foil, or any other planar separation with a PCB

See also “blister”.

[IEC 60194 (1999-04)]

dewetting

condition that results when molten solder coats a surface and then recedes to leave irregularlyshaped mounds of solder that are separated by areas that are covered with a thin film of solder and with the basis metal not exposed

[IEC 60194 (1999-04)]

flexible PCB

PCB either single, double sided or multilayer consisting of a printed circuit or printed wiring using flexible base materials only

[IEC 60194 (1999-04)]

haloing

mechanicallyinduced fracturing or delamination, on or below the surface of a base material, that is usually exhibited by a light area around holes or other machined features

[IEC 60194 (1999-04)]

high frequency PCB

PCB used for high frequency applications, that has specific requirements to the dielectric properties of the base laminates as well as special dimensional requirements to the layout for electrical purposes

inclusions

foreign particles, metallic or nonmetallic, that may be entrapped in an insulating material, conductive layer, plating, base material or solder connection

[IEC 60194 (1999-04)]

key personnel

personnel with specialist knowledge responsible for defined production or product assurance areas

measling

condition that occurs in laminated base material in which internal glass fibres are separated from the resin at the weave intersection

- 1 This condition manifests itself in the form of discrete white spots or “crosses” that are below the surface of the base material. It is usually related to thermallyinduced stress.

- 2 See also “crazing”.

[IEC 60194 (1999-04)]

metal core PCB

PCB using a metal core base material

[IEC 60194 (1999-04)]

multilayer PCB

PCB that consist of rigid or flexible insulation materials and three or more alternate printed wiring and/or printed circuit layers that have been bonded together and electrically interconnected

[IEC 60194 (1999-04)]

prepreg

sheet of material that has been impregnated with a resin and cured to an intermediate stage

Bstaged resin.

[IEC 60194 (1999-04)]

printed circuit board (PCB)

printed board that provides both pointtopoint connections and printed components in a predetermined arrangement on a common base

This includes singlesided, double sided and multilayer PCBs with rigid, flexible, and rigidflex base materials.

[IEC 60194 (1999-04)]

rigid doublesided PCB

doublesided PCB, either printed circuit or printed wiring, using rigid base materials only

[IEC 60194 (1999-04)]

rigidflex PCB

PCB with both rigid and flexible base materials

[IEC 60194 (1999-04)]

rigidflex doublesided PCB

doublesided PCB, either printed circuit or printed wiring, using combinations of rigid and flexible base materials

[IEC 60194 (1999-04)]

rigidflex multilayer PCB

multilayer PCB, either printed circuit or printed wiring, using combinations of rigid multilayer and flexible single and doublesided base materials

rigid PCB

PCB using rigid base materials only

[IEC 60194 (1999-04)]

rigid singlesided PCB

singlesided PCB, either printed circuit or printed wiring, using rigid base materials only

[IEC 60194 (1999-04)]

rigid multilayer PCB

multilayer PCB, either printed circuit or printed wiring, using rigid base materials only

[IEC 60194 (1999-04)]

scratch

narrow furrow or grove in a surface

It is usually shallow and caused by the marking or rasping of the surface with a pointed or sharp object.

[IEC 60194 (1999-04)]

sequentially laminated multilayer PCB

multilayer PCB that is formed by laminating together through hole plated doublesided or multilayer PCBs

Thus, some of its conductive layers are interconnected with blind or buried vias.

[IEC 60194 (1999-04)]

test pattern

part of the PCB that refers to the copper pattern on and within the PCB substrate for a specific test

Abbreviated terms

For the purpose of this Standard, the abbreviated terms from ECSS-S-ST-00-01 and the following apply:

|

Abbreviation

|

Meaning

|

|

CoC

|

certificate of conformance

|

|

DML

|

declared material list

|

|

n.a.

|

not applicable

|

|

PCB

|

printed circuit board

|

|

PTH

|

platedthrough hole

|

|

PTFE

|

polytetrafluoroethylene

|

|

r.m.s.

|

rootmeansquare

|

|

TBD

|

to be defined

|

Principles

For the need of this Standard the role “PCB manufacturer” as lowest level supplier has been explicitly introduced to allow proper allocation of requirements.

Requirements

Procurement of PCBs

General

The supplier shall procure PCBs from a PCB manufacturer with a qualification approval for an identified technology in conformance with ECSS-Q-ST-70-10.

The supplier can procure space quality PCBs from a PCB manufacturer with qualification approval according to ECSS-ST-Q-70-10 during the valid period of the approval.

The supplier shall perform the incoming inspection and control of the delivered PCBs.

Design and layout

The supplier and PCB manufacturer shall agree on the following issues:

- The transfer of the plotting, drilling and routing data from the supplier to the PCB manufacturer;

- The numbering system for the different issues;

This is done to avoid mistakes.

- Construction data, such as hole sizes, contours and thickness dimensions, as well as specific requirements regarding electrical requirements and dielectric properties.

The agreement between the supplier and the PCB manufacturer can be described in the specific procurement document.

The supplier shall provide the PCB manufacturer with the net list documentation with a suitable format.

The net list is used to verify that the supplier’s data files are correctly transferred to the PCB manufacturer and to set up the electrical functional testing of the finished PCBs.

The supplier shall include the manufacturing tolerances given by the PCB manufacturer when designing the PCB layout.

The tolerances and requirements for the various finished PCBs are specified in clause 7.

Multilayer PCBs shall have a layout and be built as symmetrical as possible to avoid excessive wrapage and twist.

The supplier shall use a minimum of two prepregs, between layers.

The number of electrical layers shall be an even number.

For rigidflex PCBs the customer shall order the PCB with its frame attached.

- 1 This is done in order not to stress the flexible parts during handling and mounting of components.

- 2 The frame can be detached after the assembly of the PCBs.

The PCB may be procured without the frame providing that stressing of the flexible connection is avoided.

The PCB manufacturer shall define during the design together with the supplier the amount of copper and its distribution.

An even distribution is preferred.

For surface mount technology and circuits to be wave soldered, only pads on the external layer should be used.

This is done because high density circuitry on external layers is not reliable.

The supplier shall use teardrop design for fine lines and small annular rings.

The PCB manufacturer shall not use hot air solder levelling (HAL or HASL) and infrared reflow.

These techniques can be destructive because of overheating of the PCB. Also it does not appear possible to fulfil the requirement for the tin-lead surface finish with regard to dimensions.

Before any installation of components or soldering or desoldering operations a bake-out shall be performed as specified in ECSS-Q-ST-70-08.

Base materials

Base laminate materials

The PCB manufacturer shall use materials which conform to ECSS-Q-ST-70, IEC 60249 (1993-05) and IPC-4101 Standards.

All base materials are mentioned in clause 7.

Basic metallic layer

The supplier shall design the external layer using basic copper thickness of 70 m, 35 m, 17,5 m and 9 m.

The supplier shall design the internal layers using basic copper thickness of 70 m, 35 m and 17,5 m.

For Cufoil the PCB manufacturer shall use copper quality “HTE” (IPC-MF-150F).

Plated metallic layers and finishes

Copper (electrolytic)

The PCB shall be manufactured with copper of purity of at least 99,5 %.

The copper ductility shall be at least 12 %.

A ductility of 18 % is recommended.

The PCB manufacturer shall plate the platedthrough holes with the following copper thickness:

- For soldering holes at least 25 m

- Via holes at least 20 m.

The total basic and plated copper on surface layers for soldering pads shall have a thickness of at least 40 m.

The total basic and plated copper for internal layers shall have a thickness of at least 17,5 m.

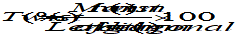

Electroplated tinlead thickness over copper

The fused tin-lead shall have a minimum thickness of 8 m in the highest part of the pad and tracks.

Before reflow the thickness of (15 7) m is recommended.

The fused tin-lead shall have a minimum thickness of 2 m on the corner of the PTH.

A fused tin-lead thickness of 1 m on the corner of the PTH can be tolerated provided that the solderability is acceptable.

The fused tin-lead shall have a thickness of 8 m on half of the height of the hole wall.

The fused tin-lead shall have a thickness of 2 m on the remaining two quarters of the hole wall.

The fused tin-lead should reflow over the edges of the copper pads and tracks.

Nickel electrolytic plating (optional) over copper plating

The electrolytic nickel plating over copper shall have a thickness from 2 m to 10 m.

Gold (electrolytic)

The PCB manufacturer shall use gold for high frequency circuits or other assembly methods when specified by the supplier.

When gold finish is needed the PCB shall be manufactured with gold of a purity of at least 99,8 %.

When gold finish is needed the PCB shall be manufactured with gold that does not contain more than 0,2 % of silver.

Alternative types of gold (e.g. for high frequency circuits) can be used, provided that the gold is proven to be satisfactory during execution of the qualification programme.

The thickness of gold over bare copper shall be between 3 m and 7 m.

The thickness of gold over nickel plating shall be between 1 m and 7 m.

If tinlead plating is applied together with gold plating on the same PCB, a tinlead overlap on gold of minimum 200 m shall be used on the surface of the PCB.

This is done in order to ensure protection of the plated copper layer.

The tin-lead overlap area shall be a minimum of 200 m distance from the termination pad designated for soldering as given in ECSS-Q-ST-70-08 clause 8.4.

Special materials

Metal core

The PCB manufacturer shall use copper - invar – copper or copper - molybdenum – copper in conformance with IPC-CF-152B.

Heatsinks: material and surface treatment

For copper, aluminium and brass heat-sinks, the PCB manufacturer shall use the material as specified by the supplier’s DML.

PCB delivery

Marking

The PCB manufacturer shall mark the PCBs as follows:

- PCB manufacturer’s logo

- PCB reference code and serial number

In the event that there is not sufficient space on the PCBs for the marking, the PCB manufacturer can ensure traceability by other means or request for waiver.

- Number of layers. Marking inks shall be as follows:

- Permanent polymer inks

- Specified in the procurement documentation

- Capable of withstanding fluxes, cleaning solvents, soldering, cleaning and coating processes encountered in later manufacturing processes according to ECSS-Q-ST-70-07, ECSS-Q-ST-70-08, ECSS-Q-ST-70-28, ECSS-Q-ST-70-38

- Conform to the outgassing requirements of ECSS-Q-ST-70-02. If a conductive marking is used, the marking shall be treated as a conductive element on the PCB.

Associated test coupons

The PCB manufacturer shall produce one associated test coupon per panel to be delivered to the supplier.

The design of the associated test coupon shall be representative of the PCBs to be delivered to the supplier.

The supplier and the PCB manufacturer shall agree on the design of the associated test coupon.

The associated test coupon shall enable:

- Testing as defined in clause 6

- Testing of insulation resistance as defined in ECSS-Q-ST-70-10 clause 7.2.8

- Continuity testing as defined in ECSS-Q-ST-70-10 clause 7.2.8

- Dielectric withstanding voltage as defined in ECSS-Q-ST-70-10 clause 7.2.8.

Outgoing inspection and PCB manufacturer data package

The PCB manufacturer shall test an in house associated test coupon to demonstrate the compliance to the inspection criteria of microsections as described in clause 6.3.

The PCB manufacturer shall not deliver a PCB for which the results on the associated test coupon present any major nonconformance as per clauses 6 and 7.

The PCB manufacturer shall deliver the data package to the supplier.

The data package shall contain the following items:

- The Certificate of conformance (CoC) in conformance with Annex A;

- Supplier specification.

Packaging

Handling and storage

PCBs shall be stored in a dry environment until they are soldered.

If assembly involves two or more steps, the supplier shall store the PCBs in between the assembly steps in containers either with desiccant or in dry nitrogen environment.

The PCBs shall be handled only with clean lintfree gloves.

Packaging

The PCBs and their associated test coupons shall be packed in order to prevent any degradation due to corrosion, deterioration or physical damage.

The PCBs shall be individually packed in a noncorrosive material.

The PCB manufacturer shall ensure safe delivery to the supplier.

The packaging shall consist of individual, air tight plastic containers.

PVC packaging shall not be used.

Desiccant or dry nitrogen filling shall be used in the packaging.

The PCB shall not be in direct contact with the desiccant.

If a desiccant is used, means for indication of moisture content shall be provided.

The PCBs and their associated test coupon shall be packed in order to avoid pressure on, or friction between the PCBs.

The containers used to ship the PCBs and the associated test coupon shall be of type and size that ensure acceptance by common carrier.

Each shipment shall include for every delivered PCB the Certificate of conformance (CoC) established in conformance with Annex A.

Each shipping container shall be marked according to supplier requirements.

Supplier acceptance of PCBs

Supplier acceptance inspection

The supplier shall inspect each of the delivered PCBs according to PCB delivery clause 5.3.

The supplier shall visually inspect each of the delivered PCBs in conformance with the procedure shown in clause 6.

The supplier shall reject a PCB in case of a major nonconformance.

The supplier shall retain the associated test coupon for at least 10 years or as otherwise specified in the project requirements.

The associated test coupon can be used for supplementary testing.

Electrical test

The supplier and the PCB manufacturer shall agree on the electrical test to be performed by the PCB manufacturer.

The PCB manufacturer shall use either the test bed electrical tester or the flying probe tester to measure the continuity and the insulation as part of functional testing.

Inspection of PCBs

General

The tests specified in this clause are a subset of the tests in ECSS-Q-ST-70-10 clause 7.

Visual inspection and nondestructive test

Verification of marking

Each board shall be inspected with the naked eye for correct marking.

The marking shall be legible and resistant to test stresses.

The nonconformance criteria shall be as follows:

- Identification impossible M

- Marking not conforming to supplier’s specification M

- Defects not affecting identifications. m

Visual aspects

Each board shall be inspected by magnification 10 with suitable lighting conditions to verify that construction and workmanship meet the requirements.

In case of any irregularity, the area shall be examined under 20 - 40 magnification.

The nonconformance criteria for the general cleanliness and contamination shall be as follows:

- Contamination visible to the naked eye and not removable by cleaning according to ECSS-Q-ST-70-08 M

- Contamination visible to the naked eye and removableby cleaning according to ECSS-Q-ST-70-08 m The nonconformance criteria for the substrate shall be as follows:

- Not in conformance with PCB manufacturer’s trademark and required quality M

- Scratches cutting glass fibre or leaving marks in the dielectric laminate that are affecting reliability M

- Scratches not affecting reliability m

- Dents, crazing and haloing:

- Visible to the naked eye M

- Only visible with magnification aids m

- Nonhomogeneity regarding colouring and opacity m/M

- Discoloured copper oxide layer on internal layer is acceptable

- Inclusion of foreign matter, blistering or air bubbles:

- Visible to the naked eye M

- Only visible with magnification aids m

- Delamination M

- Measling:

- General measling spread over the whole PCB surface M

- Local measling that causes reduction of the insulation distance in the outer layer to below the requirement M

- Local measling that does not cause reduction of the insulation distance in the outer layer to below the requirement m

- Fungus growth; M

- Delamination of cover layer (only for flexible PCB). m/M The nonconformance criteria for nonplatedthrough holes shall be as follows:

- Holes plated unintentionally m/M

- Incompletely drilled holes, missing or additional holes m/M The nonconformance criteria for the routing shall be as follows:

- Incomplete routing of board, such that dimensional or mechanical requirements are not met M

- Arbitrary cutting defects that remain acceptable within the dimensional requirements m The nonconformance criteria for the surface metallization shall be as follows:

- Conductors or pads not conforming to supplier’s specification M

- Terminal pads or conductors partially or completely missing M

- Terminal pads or conductors that are cut M

- Terminal pads or conductors forming a short circuit M

- Lifting/delamination of conductive pattern from substrate M

- Scratches in the SnPb metallisation exposing the underlaying copper plating M

- Copper or nickel visible on top surface plated areas M

Exposed copper can be accepted on the side of tracks or on the side of soldering pads.

- Large number of superficial scratches not attributed to a manufacturing process evidencing bad workmanship M

- Dewetting of fused tin lead finish on solder pads M

- Granular surface structure of fused tin lead finish on solder pads m/M

- Corrosion of exposed copper M

- Migration of underlaying copper through gold coating M The nonconformance criteria for platedthrough holes shall be as follows:

- Incompletely drilled, additional or missing holes M

- Partially or completely missing metallization M

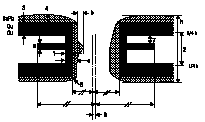

- Component holes 0,6 mm filled or partially filled with solder resulting in a diameter smaller than the requirement m/M The nonconformance criteria for arbitrary defects of conductors and terminal pads shall be as follows:

- a 20 % of x and minimum conductor width requirement m

- a 20 % of x M

- minimum conductor width requirement M

- b x m

- b x M

- Opposite peaks: if z 80 % of y M

- Isolated peaks or valleys: h 20 % of x and z requirement M

- Conducting island: a + h 20 % of y and the isolation spacing requirement M

- Minimum remaining spacing y - a requirement M

- a 20 % of y M

- b y M

- Cover layer (flexible PCBs) covering part of solder pad (see Figure 6-3) M

Intermittent and irregular metallisation defects on conductors are edge roughness (peak or valley), pits, pin holes, voids, protrusions or indentations, as shown in Figure 6-1, Figure 6-2 and Figure 6-3.

Figure 6-1: Arbitrary defects on conductors

Figure 6-2: Arbitrary defects on spacing between conductors

Figure 6-3: Misalignment of cover layer (for flexible PCBs)

Figure 6-3: Misalignment of cover layer (for flexible PCBs)

External dimensions

Each board shall be measured by means of suitable standard measuring equipment to verify that the physical dimensions, including board thickness and external dimensions meet the supplier’s specification.

The nonconformance criteria for the thickness of base laminate (average of 4 measurements on the board) shall be as follows:

- Thickness not conforming to tolerance limits of the supplier’s specification M The nonconformance criteria for the length and width of board (average of 2 measurements on the board) shall be as follows:

- Length or width not conforming to tolerance limits of the supplier’s specification M

Warp

The PCBs shall be placed unrestrained on a plane horizontal surface with the convex side upward.

The warp shall be expressed in percentage terms.

The maximum bow between the plane horizontal surface and the PCB shall be measured as defined in Figure 6-4.

The length of the PCB shall be measured.

The warp percentage shall be calculated as defined in equation [6-1]:

|

|

[6-1]

|

The nonconformance criteria shall be as follows:

- Warp requirement M

Figure 6-4: Warp

Twist

The PCB shall be placed on a plane horizontal surface so that it rests on three corners.

The twist shall be expressed in percentage terms.

The distance between the plane horizontal surface and the fourth corner of the PCB shall be measured as defined in Figure 6-5.

The length of the diagonal shall be measured.

The twist percentage shall be calculated as defined in equation [6-2].

|

|

[6-2]

|

The nonconformance criteria shall be as follows:

- Twist requirement M

Figure 6-5: Twist

Microsection inspection criteria

General

The test shall be carried out in conformance with tests 1c and 15b of IEC 60326-2-am 1 (1992-06).

For high frequency conductors the customer shall specify at which height of the conductor the width shall be measured (see Figure 6-6).

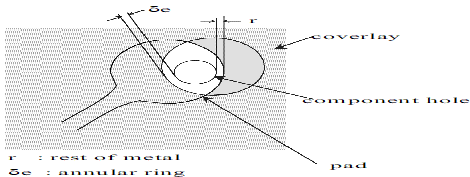

w width of conductor

w width of conductor

e minimum annular erring on external layer

e minimum annular erring on internal layer

d diameter of plated-through hole

h height of conductor

Figure 6-6: Dimensional parameters to be measured

Thickness of metalplating

The test shall be carried out on a microsection.

Observations shall be made with magnification greater than or equal to 250.

The nonconformance criteria for the thickness of copper plating on external layers shall be as follows:

- Basic copper:

- Thickness not conforming to the supplier’s specification M

- Basic copper plus electrolytic copper on nonsoldering areas:

- Thickness requirement M

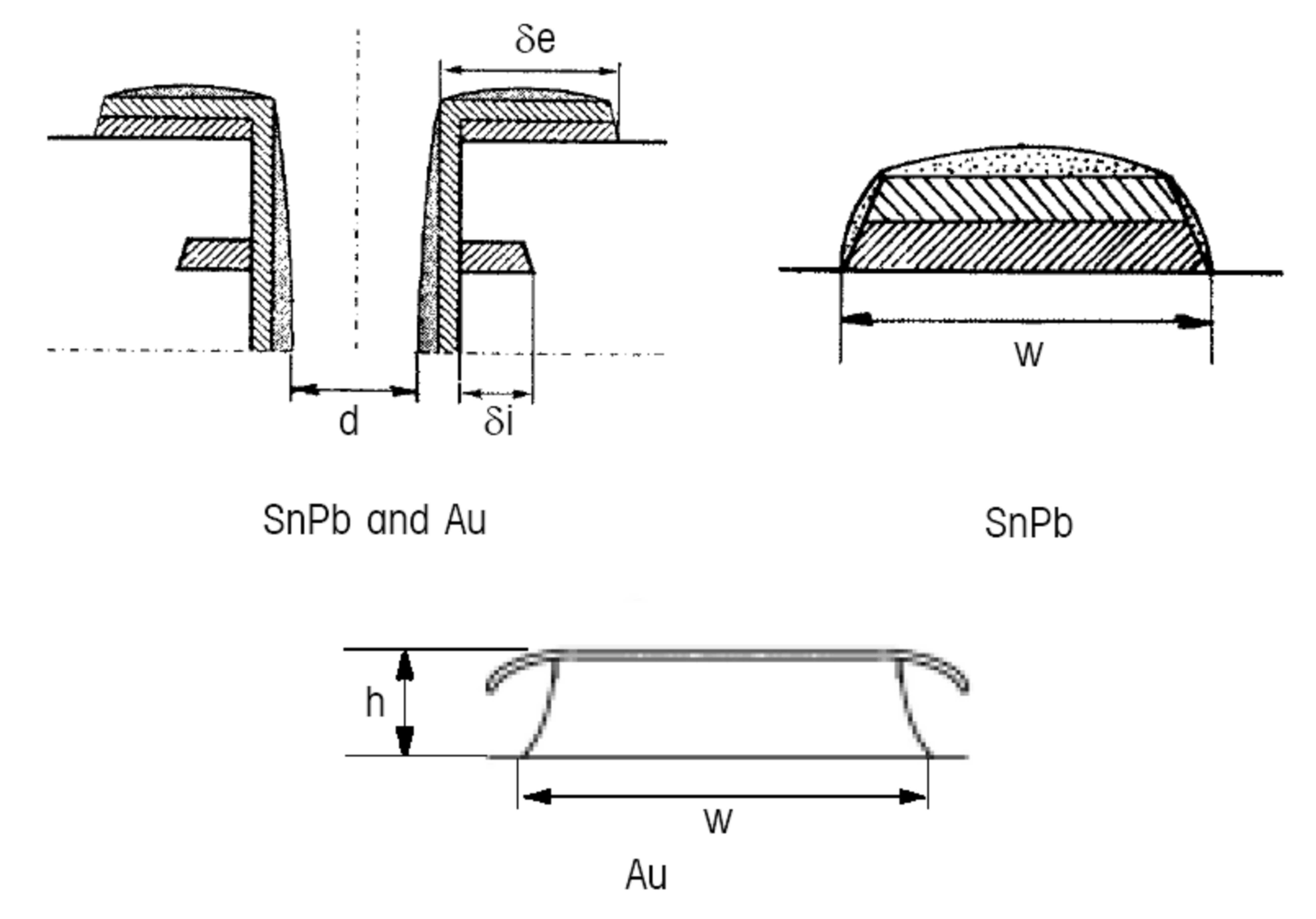

- Basic copper plus electrolytic copper soldering pads (see Figure 6-7 number 2):

- Thickness 40 m M

The nonconformance criteria for the thickness of copper in platedthrough holes that are component holes shall be as follows:

- Thickness 40 m M

- Average thickness based on 3 measurements taken on the hole walls (see Figure 6-7 number 1):

- Thickness requirement M

The nonconformance criteria for the thickness of copper layer on internal layers shall be as follows:

- Thickness requirement M

- Thickness not conforming to supplier’s specification M The nonconformance criteria for the thickness of copper in platedthrough holes that are vias, buried vias or blind vias shall be as follows:

- Thickness requirement M The nonconformance criteria for the thickness of tinlead alloy on surface, measured along the conductor longitudinal axis, shall be as follows:

- 5 m thickness 8 m m

- Thickness 5 m M The nonconformance criteria for the thickness of tinlead alloy in holes shall be as follows:

- In highest part of half of the hole wall height (see Figure 6-7 number 3): thickness 8 m M

- On angle of hole corner (see Figure 6-7 number 4):1 m thickness 2 m m

- On angle of hole corner (see Figure 6-7 number 4):thickness 1 m M

Key

Key

1 = Cu in PTH

2 = Cu at surface pattern

3 = SnPB in hole

4 = SnPb in angle area

internal buging b < a

Figure 6-7: Microsection of a PTH

The nonconformance criteria for the thickness of electrolytic Au or Au/Ni on surface and in holes (measured along the conductor longitudinal axis) shall be as follows:

- Au for manual soldering on nickel:

- Thickness 1 m M

- Thickness 7 m M

- Au for manual soldering on copper:

- Thickness 3 m M

- Thickness 7 m M

- Au for high frequency circuits or other assembly methods as specified by customer:

- Thickness not conforming to tolerance limits of supplier’s specification M

- Ni:

- Thickness 2 m M

- Thickness 10 m M

The nonconformance criteria for the distance between SnPb and Au overlap and the termination pad designated for soldering shall be as follows:

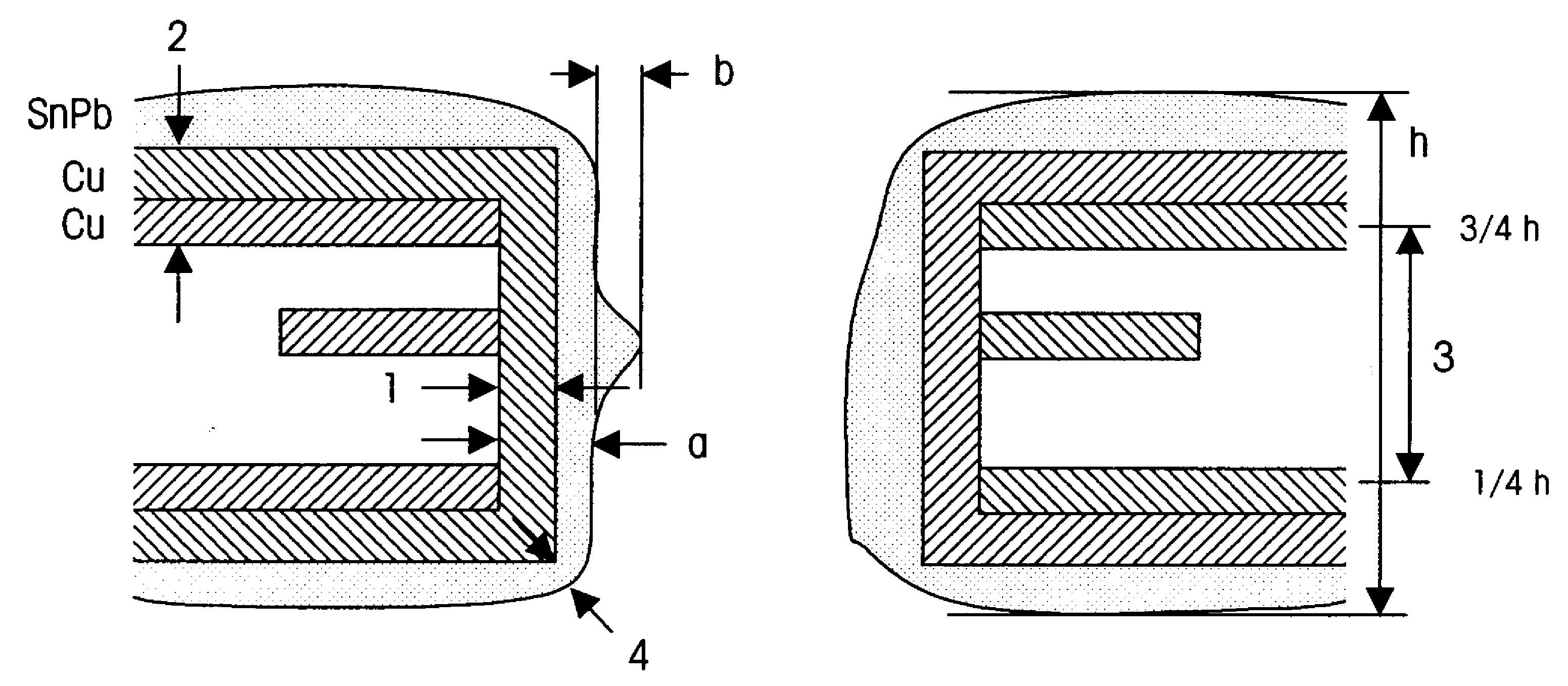

- Distance 200 m M The nonconformance criteria for the etch undercut on external and internal layers for fused SnPb (see Figure 6-8) shall be as follows:

- Undercut (u) total copper thickness (h) M The nonconformance criteria for the etch undercut on external and internal layers for Au plating with or without Ni finish (see Figure 6-9) shall be as follows:

- If undercut (d) 30 m M The nonconformance criteria for the etch overhang on external layers for Au plating with or without Ni finish (see Figure 6-10) shall be as follows:

- If overhang (D) 2 thickness of total copper M

For high frequency application overhang is normally undesirable and can be removed mechanically.

Figure 6-8: Undercut for PCBs with fused SnPb finish

Figure 6-9: Undercut for PCBs with Au/Ni or Au finish

Figure 6-10: Overhang for PCBs with Au/Ni or Au finish

Aspect of platedthrough holes

Sections of platedthrough holes shall be observed with magnification greater than or equal to 100.

Layer misregistration compared to the minimum annular ring on pads.

The nonconformance criteria for the layer misregistration on the external layer (see Figure 6-6) shall be as follows:

- e requirement M The nonconformance criteria for the layer misregistration on the internal layers (see Figure 6-6) shall be as follows:

- i requirement M

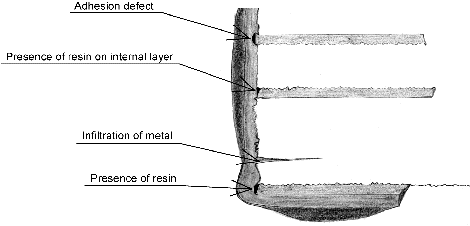

- Minimum insulation between layers requirement M The nonconformance criteria for irregular drilling (see Figure 6-11) shall be as follows:

- Infiltration of metal into base laminate:

- 40 m infiltration 80 m m

- Infiltration 80 m M

- Presence of adhesive on basic copper not leading to rupture during fusing process or thermal shock m

- Adhesion defects between metalplating and basic copper M

- Adhesion defects between metalplating and inner layers M

- Resin smear on the interface between internal conductor and plated copper greater than 15 % of conductor thickness M

- Void in resin greater than 50 % of basic copper thickness. M

Figure 6-11: Microsection in PTH: Possible defects

Figure 6-11: Microsection in PTH: Possible defects

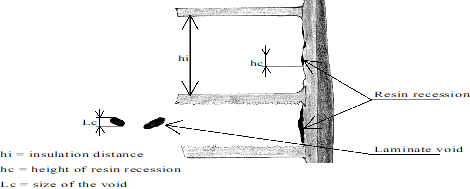

The nonconformance criteria for voids in PCB base laminate substrate and resin recession in holes (see Figure 6-12) shall be as follows:

- Voids in the PCB base laminate substrate:

- Lc 80 m M

- At edge of metalplating:

- Sum of resin recession hc 20 % sum hi � M

- Resin recession in hole before or after test:

- Resin recession between 10 % and 20 % of height of hole m

- If resin recession 20 % of height of hole M

The nonconformance criteria for the copper plating inside buried, blind, via and component holes shall be as follows:

- Void in copper plating in holes M

The nonconformance criteria for the resin inside buried vias shall be in conformance with Figure 6-13.

Figure 6-12: Microsection of PTH: Possible defects

Figure 6-12: Microsection of PTH: Possible defects

Figure 6-13: Voids in resin inside buried vias

Requirements for PCBs

Rigid singlesided and doublesided PCBs

The base materials shall be in conformance with ECSS-Q-ST-70, IEC specifications and IPC-4101 and shall be one of the following:

- Woven-glass-reinforced epoxy resin FR4;

- Woven-glass-reinforced polyimide resin. The limits for the dimensional characteristics shall be as follows:

- External dimension tolerance: 0,2 mm;

- Thickness tolerance: 10 %;

- Active board size, maximum: supplier’s specification;

- Board thickness maximum: 3,2 mm;

- Positioning tolerance between registration mark and edge of circuit: 0,2 mm;

- Conductor width: 200 m minimum (for fine pitch 120 m width is tolerated if less than 5 mm from component pad);

- Spacing between conductors: 300 m minimum (for fine pitch 150 m spacing is tolerated if less than 5 mm from component pad);

- Conductor tolerance (minimum/maximum): supplier’s specification, 20 % maximum;

- Tolerance on diameter of terminal pads: supplier’s specification, 20 % maximum;

- Minimum hole diameter:

- Component hole: in conformance with ECSS-Q-ST-70-08;

- Via hole: 0,25 mm minimum and maximum aspect ratio t/d = 6;

- Tolerance on diameter of platedthrough holes:

- Nominal 0,7 mm: maximum 0,15 mm for component hole;

- Nominal 0,7 mm: maximum 0,20 mm;

- Tolerance on diameter of nonplatedthrough holes: maximum 0,20 mm;

- Positioning tolerance of holes with respect to reference mark: 0,1 mm;

- Relative misregistration pad/hole: 0,15 mm;

- Misalignment determined by measuring minimum annular ring:

- Solder side: 0,20 mm;

- Component side (reduced pads): 0,10 mm;

- Nonsoldering hole: 0,10 mm.

The limits for the electrolytic coatings are as follows:

- Electrolytic copper plating:

- Minimum purity: 99,5 %;

- Thickness of surface pattern: 25 m;

- Thickness of platedthrough holes: 25 m;

- Thickness of via holes: 20 m;

- Tin lead plating after reflow:

- Tin content of alloy: (63 8) %;

- Thickness on surface: 8 m in highest part;

- Thickness in platedthrough holes: 8 m in highest part (minimum half height of hole wall);

- Thickness on corner angle: 2 m;

- Electrolytic gold plating:

- Minimum purity: 99,8 % (not more than 0,2 % silver);

- Thickness on nickel: (4 3) m;

- Thickness on copper: (5 2) m;

- Electrolytic nickel plating:

- Thickness: 2 m to 10 m.

Electrolytic nickel plating is optional under gold.

The limits for the mechanical characteristics are as follows:

- Warp and twist: 1,1 % for board thickness 1,6 mm, 1,5 % for board thickness 1,6 mm;

- Conductor adhesion/peel strength:

- On epoxy: 16 N/cm;

- On polyimide: 12 N/cm;

- Pull strength:

- For terminal pads 4 mm on epoxy: 140 N;

- For terminal pads 4 mm on polyimide: 80 N;

- For terminal pads 2 mm on epoxy: 35 N;

- For terminal pads 2 mm on polyimide: 20 N.

The limits for the electrical characteristics are as follows:

- Insulation resistance:

- Intralayer (i.e. in the same layer): 104 M;

- Interlayer (i.e. between opposite layers): 105 M;

- Withstanding voltage per mm spacing between conductors:

- Intralayer and interlayer: 1 000 V r.m.s;

- Short time overload:

- 0,035 mm copper thickness: 7 A for 4 s;

- 0,070 mm copper thickness: 14 A for 4 s;

- Long time overload, destructive current:

- 0,035 mm copper thickness: I 8 A;

- 0,070 mm copper thickness: I 16 A.

Rigid singlesided and doublesided PCBs for high frequency application

The base materials shall be in conformance with ECSS-Q-ST-70, IEC specifications and IPC-4101 and shall be on of the following:

- Randomglassreinforced PTFE resin with or without Al backing;

- Wovenglassreinforced PTFE resin;

- Ceramic filled wovenglassreinforced PTFE resin;

- Ceramic filled PTFE resin with or without Al backing;

- Ceramic filled cross-linked hydrocarbon/thermoset polymer;

- Wovenglassreinforced epoxy resin FR4;

- Quartz filled polyimide resin. The limits for the dimensional characteristics shall be as follows:

- External dimension tolerance: 0,2 mm;

- Thickness tolerance: 10 %;

- Active board size, maximum: supplier’s specification;

- Board thickness (minimum/maximum): customer’s and supplier’s specification according to electrical performance;

- Positioning tolerance between registration mark and edge of circuit: 0,2 mm;

- Conductor width/spacing: customer’s and supplier’s specification according to electrical performance;

- Tolerance on conductor (minimum/maximum): supplier’s specification;

- Tolerance on diameter of terminal pads: customer’s and supplier’s specification according to electrical performance;

- Minimum hole diameter:

- Component hole: in conformance with ECSS-Q-ST-70-08;

- Via hole: 0,25 mm minimum and maximum aspect ratio t/d = 6;

- Tolerance on diameter of platedthrough holes:

- Nominal 0,7: maximum 0,15 mm for component hole;

- Nominal 0,7: maximum 0,20 mm;

- Tolerance on diameter of nonplatedthrough holes: maximum 0,20 mm;

- Positioning tolerance of holes with respect to reference mark: 0,1 mm;

- Relative misregistration pad/hole: 0,15 mm;

- Misalignment determined by measuring minimum annular ring:

- Solder side: 0,2 mm;

- Component side (reduced pads): 0,1 mm;

- Nonsoldering hole: 0,1 mm.

The limits for the electrolytic coatings shall be as follows:

- Electrolytic copper plating:

- Minimum purity: 99,5 %;

- Thickness of surface pattern for soldering pads: 25 m (total thickness of basic plus electrolytic copper 40 m);

- Thickness of platedthrough holes: 25 m;

- Thickness of via hole: 20 m;

- Tin lead plating after reflow:

- Tin content of alloy: (63 8) %;

- Thickness on surface: 8 m in highest part;

- Thickness in platedthrough holes: 8 m in highest part (minimum half height of hole wall);

- On corner angle: 2 m;

- Electrolytic gold plating:

- Minimum purity: 99,8 %

- Not containing more than 0,2 % silver;

- Thickness on nickel: 1 m to 7 m;

- Electrolytic nickel plating:

Optional under gold.

* Thickness: 2 m to 10 m;

The limits for the mechanical characteristics shall be as follows:

- Warp and twist:

- Randomglassreinforced PTFE resin: n.a.;

- Wovenglassreinforced PTFE resin: n.a.;

- Ceramic filled PTFE resin: 1,1 %;

- Ceramic filled xlinked hydrocarbon/thermoset polymer: 1,1 %;

- Wovenglassreinforced epoxy resin FR4: 1,1 % for board thickness 1,6 mm, 1,5 % for board thickness 1,6 mm;

- Quartz filled polyimide: 1,1 % for board thickness 1,6 mm, 1,5 % for board thickness 1,6 mm;

- Conductor adhesion/peel strength:

- On PTFE reinforced/ceramic filled or nonfilled: 8 N/cm;

- Cross-linked hydrocarbon: 8 N/cm;

- On epoxy: 16 N/cm;

- On polyimide quartz: 12 N/cm;

- Pull strength:

- For terminal pads 4 mm on PTFE reinforced/ceramic filled or nonfilled: 60 N;

- For terminal pads 4 mm cross-linked hydrocarbon: 60 N;

- For terminal pads 4 mm on epoxy: 140 N;

- For terminal pads 4 mm on polyimide quartz: 60 N;

- For terminal pads 2 mm on PTFE reinforced /ceramic filled or nonfilled: 12 N;

- For terminal pads 2 mm cross-linked hydrocarbon: 12 N;

- For terminal pads 2 mm on epoxy: 35 N;

- For terminal pads 2 mm on polyimide quartz: 20 N.

The limits for the electrical characteristics shall be as follows:

- Insulation resistance:

- Intralayer: 104 M;

- Interlayer: 105 M;

- Withstanding voltage per mm spacing between conductors:

- Intralayer and interlayer: 1 000 V r.m.s.;

- Short time overload:

- 0,009 mm copper thickness: n.a.;

- 0,017 mm copper thickness: n.a.;

- 0,035 mm copper thickness: 7 A for 4 s;

- 0,070 mm copper thickness: 14 A for 4 s;

- Long time overload, destructive current:

- 0,009 mm copper thickness: n.a.;

- 0,017 mm copper thickness: n.a.;

- 0,035 mm copper thickness: I 8 A;

- 0,070 mm copper thickness: I 16 A;

- Permittivity: customer’s and supplier’s specification according to electrical performance;

- Loss angle Tg customer’s and supplier’s specification according to electrical performance.

Flexible PCBs

The base materials shall be in conformance with ECSS-Q-ST-70, IEC specifications and IPC-4101 and shall be the following:

- Flexible copperclad polyimide film. The limits for the dimensional characteristics shall be as follows:

- External dimension tolerance: 0,4 mm;

- Thickness tolerance: 20 %;

- Active board size, maximum: supplier’s specification;

- Board thickness maximum: 0,4 mm;

- Positioning between registration mark and edge of circuit: 0,4 mm;

- Conductor width/spacing: (250 m/250 m) minimum;

- Conductor tolerance (minimum/maximum): supplier’s specification;

- Tolerance on diameter of terminal pads: supplier’s specification;

- Minimum diameter of platedthrough holes: 0,25 mm;

- Tolerance on diameter of platedthrough holes for components:

- Nominal 0,7: maximum 0,15 mm;

- Nominal 0,7: maximum 0,20 mm;

- Tolerance on diameter of nonplatedthrough holes: maximum 0,20 mm;

- Positioning of holes with respect to reference mark: 0,10 mm;

- Relative misregistration pad/hole: 0,15 mm;

- Registration of sides: 0,10 mm;

- Cutting of insulation coating tolerance:

- Internal cutting: 0,50 mm;

- Misalignment determined by measuring minimum annular ring:

- Solder side: 0,25 mm;

- Reduced terminal pads (oblong): 0,10 mm;

- Nonsoldering holes: 0,10 mm;

- Misalignment of insulation coating determined by measuring rest of metal:

- Platedthrough holes: 0,15 mm;

- Nonplatedthrough holes: 0,25 mm;

- Number of layers: 2. The limits for the electrolytic coatings shall be as follows:

- Electrolytic copper plating:

- Minimum purity: 99,5 %;

- Thickness of surface pattern: 25 m;

- Thickness of platedthrough holes: 25 m;

- Tin lead plating after reflow:

- Tin content of alloy: (63 8) %;

- Thickness on surface: 8 m in highest part;

- Thickness in platedthrough holes: 8 m in highest part (minimum half height of hole wall);

- On corner angle: 2 m.

The limits for the mechanical characteristics shall be as follows:

- Conductor adhesion/peel strength: 10 N/cm;

- Pull strength:

- For terminal pads 4 mm : 60 N;

- For terminal pads 2 mm : 12 N;

- Resistance to bending cycles: 250 cycles;

- Bending test for rigidflex boards: 25 cycles. The limits for the electrical characteristics shall be as follows:

- Insulation resistance:

- Intralayer: 104 M;

- Interlayer: 105 M;

- With temperature at 80 C: 102 M;

- Withstanding voltage per mm spacing between conductors: 1 000 V r.m.s.;

- Short time overload: 7 A for 4 s;

- Long time overload, destructive current: 8 A.

Rigidflex PCBs

The requirements for rigidflex PCBs shall be in conformance with clause 7.3 for the flexible part and clause 7.5 for the rigid part.

For the construction of multilayer rigidflex the flexible copper clad polyimide film shall be without adhesive

Rigid multilayer PCBs

The base materials shall be in conformance with ECSS-Q-ST-70, IEC specifications and IPC-4101 and shall be one of the following:

- Wovenglassreinforced epoxy resin;

- Wovenglassreinforced polyimide resin;

- Wovenglassreinforced bismaleimide/trazine modified epoxy (HTg) resin;

- Nonwoven aramidereinforced polyimide resin. The limits for the dimensional characteristics shall be as follows:

- External dimension tolerance 0,2 mm;

- Thickness tolerance: 10 %;

- Maximum active board size: supplier’s specification;

- Maximum board thickness: 3,2 mm;

- Positioning between registration mark and edge of circuit: 0,2 mm;

- Conductor width:

- Internal: 120 m minimum;

- External: 200 m minimum (for fine pitch 120 m width is tolerated if less than 5 mm from component pad);

- Conductor spacing:

- Internal: 150 m minimum;

- External: 300 m minimum (for fine pitch 150 m spacing is tolerated if less than 5 mm from component pad);

- Conductor tolerance (minimum/maximum): supplier’s specification;

- Tolerance on diameter of terminal pads: supplier’s specification;

- Minimum drilled hole diameter:

- Component hole: in conformance with ECSS-Q-ST-70-08;

- Via hole: 0,25 mm minimum and maximum aspect ratio t/d = 6;

- Tolerance on diameter of platedthrough holes:

- Nominal 0,7: maximum 0,15 mm for component hole;

- Nominal 0,7: maximum 0,20 mm;

- Tolerance on diameter of nonplatedthrough holes: maximum 0,20 mm;

- Positioning of holes with respect to reference mark: 0,1 mm;

- Relative misregistration pad/hole: 0,15 mm;

- Misalignment determined by measuring minimum annular ring:

- External layers: solder side: 0,20 mm

- External layers: component side (reduced pads): 0,10 mm

- External layers: nonsoldering hole: 0,10 mm

- Internal layers: 50 m;

- Layer to layer registration: 100 m;

- Number of layers: 18 maximum. The limits for the electrolytic coatings shall be as follows:

- Electrolytic copper plating:

- Minimum purity: 99,5 %;

- Thickness of surface pattern: 25 m;

- Thickness of platedthrough holes: 25 m;

- Thickness of via holes: 20 m;

- Tin lead plating after reflow:

- Tin content of alloy: (63 8) %;

- Thickness on surface: 8 m in highest part;

- Thickness in platedthrough holes: 8 m in highest part (minimum half height of hole wall);

- On corner angle: 2 m;

- Electrolytic gold plating:

- Minimum purity: 99,8 %

- Not containing more than 0,2 % silver;

- Thickness on nickel: (4 3) m;

- Thickness on copper: (5 2) m;

- Electrolytic nickel plating:

Optional under gold.

* Thickness: 2 m to 10 m;

- Insulation between layers: 70 m minimum. The limits for the mechanical characteristics shall be as follows:

- Warp and twist: 1,1 % for board thickness 1,6 mm, 1,5 % for board thickness 1,6 mm;

- Conductor adhesion/peel strength:

- On epoxy with Tg 160 C: 16 N/cm;

- On epoxy with Tg 180 C: 12 N/cm;

- On polyimide: 12 N/cm;

- On bismaleimide/trazine modified epoxy HTg: 12 N/cm;

- Aramide/polyimide: 6 N/cm;

- Bond strength/pull strength:

- For terminal pads 4 mm on epoxy Tg 160 C: 140 N;

- For terminal pads 4 mm on epoxy Tg 180 C: 80 N;

- For terminal pads 4 mm on polyimide: 80 N;

- For terminal pads 4 mm on bismaleimide/trazine modified epoxy HTg: 60 N;

- For terminal pads 4 mm on aramide/polyimide: 60 N;

- For terminal pads 2 mm on epoxy Tg 160 C: 35 N;

- For terminal pads 2 mm on epoxy Tg 180 C: 20 N;

- For terminal pads 2 mm on polyimide: 20 N;

- For terminal pads 2 mm on bismaleimide/trazine modified epoxy HTg: 12 N;

- For terminal pads 2 mm on aramide/polyimide: 12 N.

The limits for the electrical characteristics shall be as follows:

- Insulation resistance:

- Intralayer: 104 M;

- Interlayer: 105 M;

- Withstanding voltage per mm spacing between conductors:

- Intralayer and interlayer: 1 000 V r.m.s.;

- Short time overload:

- 35 m copper thickness: 7 A for 4 s;

- 70 m copper thickness: 14 A for 4 s;

- Long time overload, destructive current:

- 35 m copper thickness: I 8 A;

- 70 m copper thickness: I 16 A;

- Internal short circuit:

- Insulation resistance: 103 M.

Sequential rigid multilayer PCBs

The base materials shall be in conformance with ECSS-Q-ST-70, IEC specifications and IPC-4101 and shall be one of the following:

- Wovenglassreinforced epoxy resin;

- Wovenglassreinforced polyimide resin;

- Wovenglassreinforced bismaleimide/trazine modified epoxy (HTg) resin;

- Nonwovenaramidereinforced polyimide resin. The limits for the dimensional characteristics shall be as follows:

- External dimension tolerance: 0,2 mm;

- Thickness tolerance: 10 %;

- Maximum active board size: supplier’s specification;

- Maximum board thickness: 3,2 mm;

- Positioning between registration mark and edge of circuit: maximum 0,20 mm;

- Conductor width:

- Internal: 120 m minimum;

- External: 200 m minimum (for fine pitch 120 m width is tolerated if less than 5 mm from component pad);

- Conductor spacing:

- Internal: 150 m minimum;

- External: 300 m minimum (for fine pitch 150 m spacing is tolerated if less than 5 mm from component pad);

- Conductor tolerance (minimum/maximum): supplier’s specification;

- Tolerance on diameter of terminal pads: supplier’s specification;

- Minimum drilled hole diameter:

- Component hole: in conformance with ECSS-Q-ST-70-08;

- Via hole: 0,25 mm minimum and maximum aspect ratio t/d = 6;

- Buried via: supplier’s specification and maximum aspect ratio t/d = 6;

- Blind via produced sequentially: supplier’s specification and maximum aspect ratio t/d = 6;

- Tolerance on diameter of platedthrough holes:

- Nominal 0,7: maximum 0,15 mm for component hole;

- Nominal 0,7: maximum 0,20 mm;

- Tolerance on diameter of nonplatedthrough holes: maximum 0,20 mm;

- Positioning of holes with respect to reference mark: 0,10 mm;

- Relative misregistration pad/hole: 0,15 mm;

- Misalignment determined by measuring minimum annular ring:

- External layers: solder side: 0,20 mm;

- External layers: component side (reduced pads): 0,10 mm;

- External layers: nonsoldering hole: 0,10 mm;

- Internal layers: 0,05 mm;

- Layer to layer registration: 100 m;

- Number of layers: 18 maximum. The limits for the electrolytic coatings shall be as follows:

- Electrolytic copper plating:

- Minimum purity: 99,5 %;

- Thickness of surface pattern: 25 m;

- Thickness of platedthrough holes: 25 m;

- Thickness of via holes: 20 m;

- Thickness of buried via holes: 18 m;

- Thickness of blind via holes: 18 m;

- Tin lead plating after reflow:

- Tin content of alloy: (63 8) %;

- Thickness on surface: 8 m in highest part;

- Thickness in platedthrough holes: 8 m highest part (minimum half height of hole wall);

- On corner angle: 2 m;

- Electrolytic gold plating:

- Minimum purity: 99,8 %

- Not containing more than 0,2 % silver;

- Thickness on nickel: (4 3) m;

- Thickness on copper: (5 2) m;

- Electrolytic nickel plating:

- Thickness: 2 m to 10 m;

Electrolytic nickel plating is optional under gold.

- Resin fill in buried vias: see 6.3.3h;

- Insulation between layers: 70 m minimum. The limits for the mechanical characteristics shall be as follows:

- Warp and twist: 1,1 % for board thickness 1,6 mm, 1,5 % for board thickness 1,6 mm;

- Conductor adhesion/peel strength:

- On epoxy with Tg 160 C: 16 N/cm;

- On epoxy with Tg 180 C: 12 N/cm;

- On polyimide: 12 N/cm;

- On bismaleimide/trazine modified epoxy HTg: 12 N/cm;

- Aramide/polyimide: 6 N/cm;

- Bond strength/pull strength:

- For terminal pads 4 mm on epoxy Tg 160 C: 140 N;

- For terminal pads 4 mm on epoxy Tg 180 C: 80 N;

- For terminal pads 4 mm on polyimide: 80 N;

- For terminal pads 4 mm on bismaleimide/trazine modified epoxy HTg: 60 N;

- For terminal pads 4 mm on aramide/polyimide: 60 N;

- For terminal pads 2 mm on epoxy Tg 160 C: 35 N;

- For terminal pads 2 mm on epoxy Tg 180 C: 20 N;

- For terminal pads 2 mm on polyimide: 20 N;

- For terminal pads 2 mm on bismaleimide/trazine modified epoxy HTg: 12 N;

- For terminal pads 2 mm aramide/polyimide: 12 N.

The limits for the electrical characteristics shall be as follows:

- Insulation resistance:

- Intralayer: 104 M;

- Interlayer: 105 M;

- Withstanding voltage per mm spacing between conductors:

- Intralayer and interlayer: 1 000 V r.m.s.;

- Short time overload:

- 0,035 mm copper thickness: 7 A for 4 s;

- 0,070 mm copper thickness: 14 A for 4 s;

- Long time overload, destructive current:

- 0,035 mm copper thickness: I 8 A;

- 0,070 mm copper thickness: I 16 A;

- Internal short circuit:

- Insulation resistance: 103 M.

ANNEX(normative)PCB Certificate of conformance (CoC) – DRD

DRD identification

Requirement identification and source document

This DRD is called from ECSS-Q-ST-70-11, requirements 5.3.3d.1 and 5.4.2k.

Purpose and objective

The purpose of the DRD is to describe the content of the PCB Certificate of conformance (CoC) document.

Expected response

Scope and content

Contents

The PCB CoC shall contain the following items:

- List of base materials used;

- Results of tests and inspections;

- Associated test coupon (one per panel);

- Microsection of as received platedthrough holes (one per panel);

- Any approved nonconformance with the above specifications.

Special remarks

The example PCB CoC document in Figure A-1 may be used.

|

Certificate of conformance

| |||||||

|

Ref. specification:

|

Order no.:

| ||||||

|

Customer:

|

Conf. no.:

| ||||||

|

PCB no.:

|

File no.:

| ||||||

|

Microsection from appropriate test coupon. Result in microns.

| |||||||

|

|

|

Min.

|

Max.

|

Remarks

| |||

|

1. Cu in PTH

|

|

|

|

||||

|

2. Sn/Pb in hole

|

|

|

|

||||

|

3. Cu on surface pattern

|

|

|

|

||||

|

4. Sn/Pb on surface pattern

|

|

|

|

||||

|

5. Sn/Pb in angle area

|

|

|

|

||||

|

6. Cu on internal layers

|

|

|

|

||||

|

7. Insulation distance

|

|

|

|

||||

|

8. Internal bulging b < a

|

|

|

|

||||

|

9. Misregistration

|

|

|

|

||||

|

Visual and dimensional inspection

| |||||||

|

Examination of base laminate

|

|

External dimensions

|

|

||||

|

Examination of conductive pattern

|

|

Dimensions of holes

|

|

||||

|

Tests

| |||||||

|

Tape test

|

|

Dielectric withstanding voltage1 000 V AC/mm

|

|

||||

|

Bond strength

|

|

Current carrying capacity 10 A 4 s

|

|

||||

|

Peel strength

|

|

Heat sink high voltage test

|

|

||||

|

Insulation resistance (layer):

|

|

Solderability

|

|

||||

|

- Within > 1 000 M at 500 V DC

|

|

Thermal stress

|

|

||||

|

- Between > 100 000 M at 500 V DC

|

|

Rework simulation test

|

|

||||

|

Bow and twist

|

|

Flexible test

|

|

||||

|

|

|

Electrical test

|

|

||||

|

Remarks:

| |||||||

|

This is to certify that the material on your subject order, shipped from our plant has been processed, inspected and found in accordance with all specifications referred to on your drawing or purchase order.We further certify that appropriate records or certificates are on file for your examination upon request.

| |||||||

|

Inspected QC:

|

Approved PA:

| ||||||

Figure: Example of a PCB CoC

Bibliography

|

ECSS-S-ST-00

|

ECSS system – Description, implementation and general requirements

|

|

IEC 60194 (1999-04)

|

Printed board design, manufacture and assembly — Terms and definitions

|