Space product assurance

High reliability assembly for surface mount and through hole connections

Foreword

This Standard is one of the series of ECSS Standards intended to be applied together for the management, engineering, product assurance and sustainability in space projects and applications. ECSS is a cooperative effort of the European Space Agency, national space agencies and European industry associations for the purpose of developing and maintaining common standards. Requirements in this Standard are defined in terms of what shall be accomplished, rather than in terms of how to organize and perform the necessary work. This allows existing organizational structures and methods to be applied where they are effective, and for the structures and methods to evolve as necessary without rewriting the standards.

This Standard has been prepared by the ECSS-Q-ST-70-61C Working Group, reviewed by the ECSS Executive Secretariat and approved by the ECSS Technical Authority.

Precedence

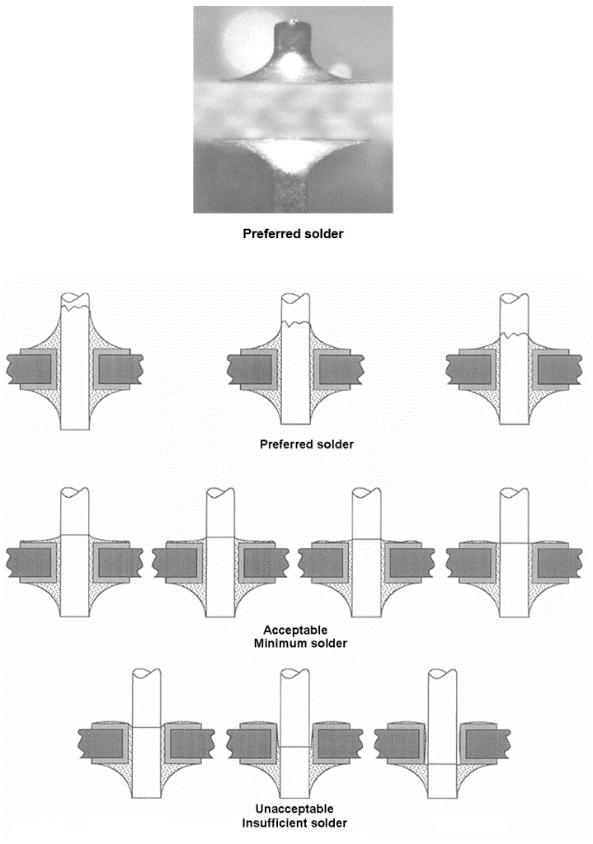

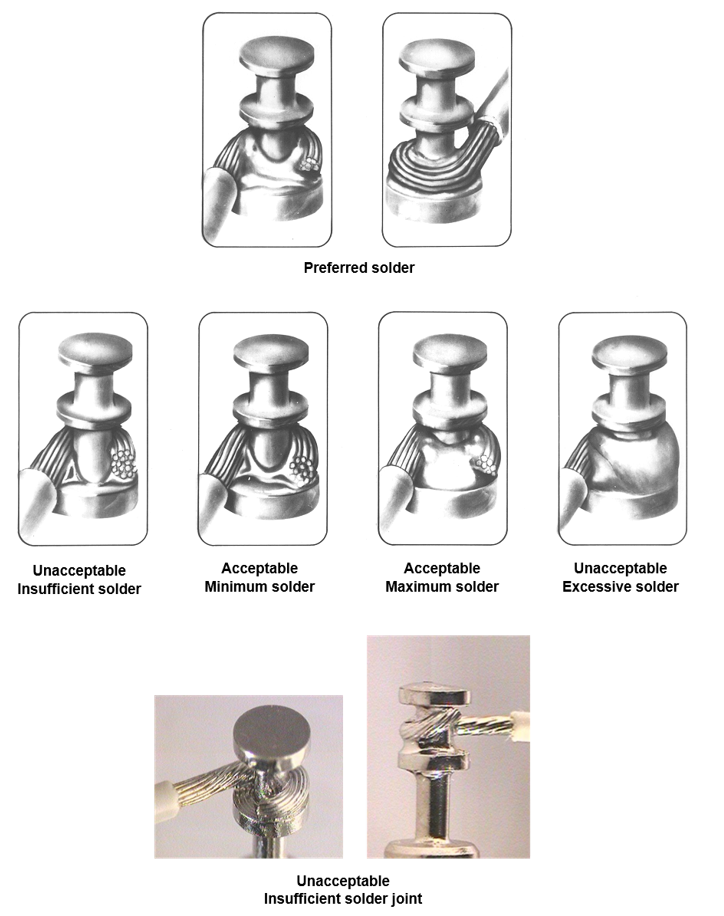

Line drawings and illustrations are depicted herein to assist in the interpretation of the written requirements of this standard. The text takes precedence over the figures.

Disclaimer

ECSS does not provide any warranty whatsoever, whether expressed, implied, or statutory, including, but not limited to, any warranty of merchantability or fitness for a particular purpose or any warranty that the contents of the item are error-free. In no respect shall ECSS incur any liability for any damages, including, but not limited to, direct, indirect, special, or consequential damages arising out of, resulting from, or in any way connected to the use of this Standard, whether or not based upon warranty, business agreement, tort, or otherwise; whether or not injury was sustained by persons or property or otherwise; and whether or not loss was sustained from, or arose out of, the results of, the item, or any services that may be provided by ECSS.

Published by: ESA Requirements and Standards Section ESTEC, P.O. Box 299, 2200 AG Noordwijk The NetherlandsCopyright: 2022© by the European Space Agency for the members of ECSS## Change log

|

ECSS-Q-ST-70-61C

|

First issue

|

Introduction

This document defines the technical requirements and quality assurance provisions for the manufacture and verification of high-reliability electronic circuits of surface mount, through hole, solderless assemblies, and soldering of harness and wire interconnection, for space applications, launchers, and associated equipment.

In the following table, principal types of through hole components and SMDs, including examples, can be gathered in the following families.

In the text of this document the term “component” is used instead of “device”.

|

THROUGH HOLE COMPONENTS (non exhaustive list) |

|

|

Radial component

|

|

|

Axial component

|

|

|

Stacked capacitors

|

|

|

TO Metal Can package

|

|

|

TO Metal tab package

|

|

|

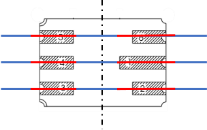

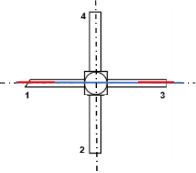

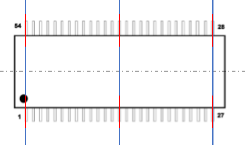

Dual in Line Package (DIL or DIP)

|

|

|

Connectors

|

|

|

Leaded magnetics

|

|

|

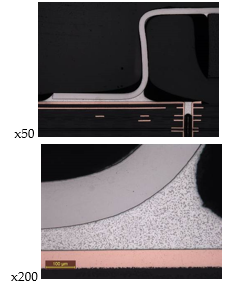

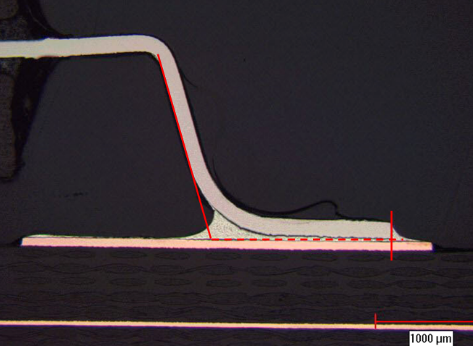

Sculptured flex

|

|

|

SMT COMPONENTS (non exhaustive list) |

|

|

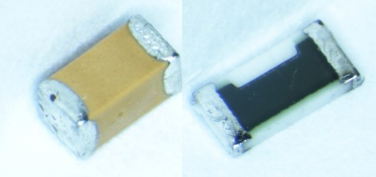

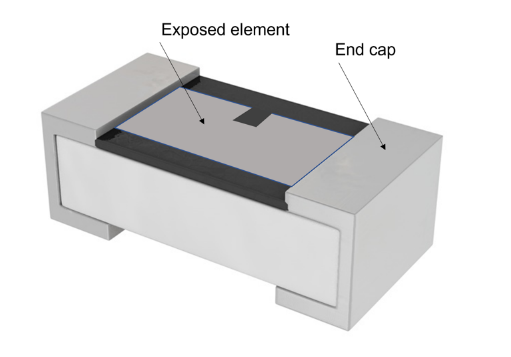

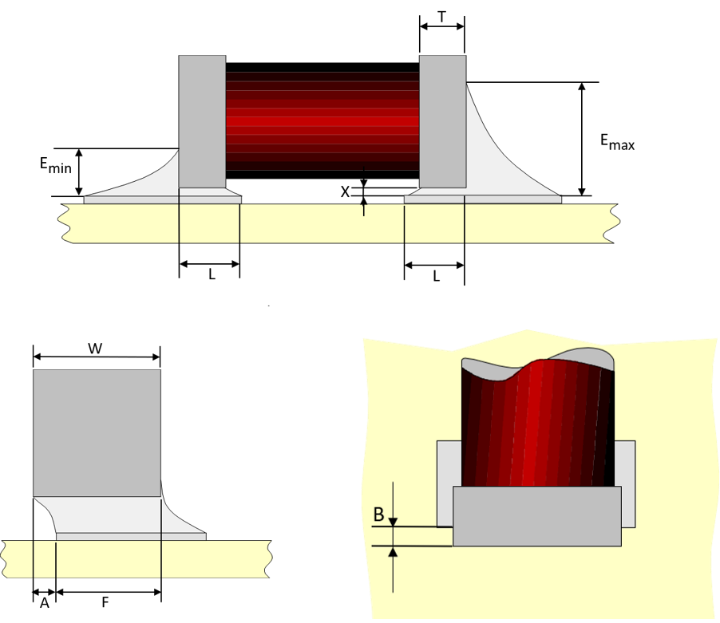

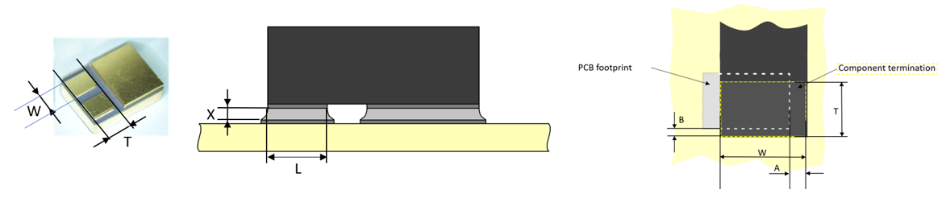

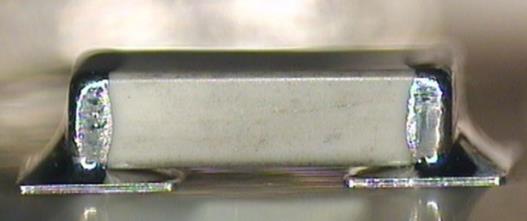

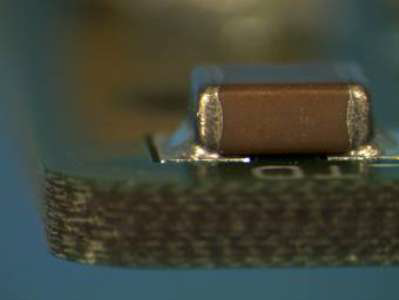

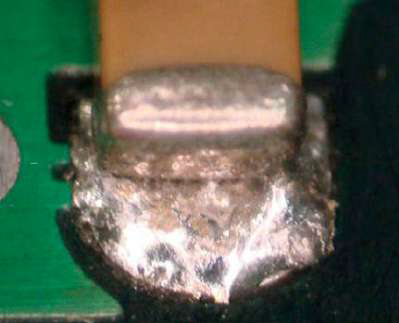

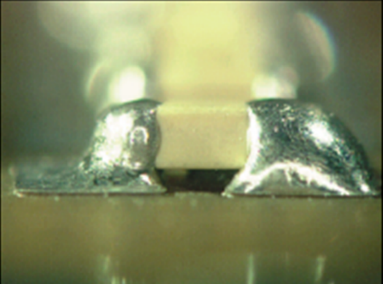

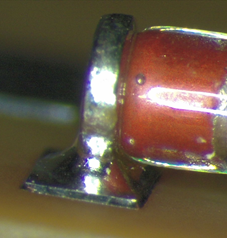

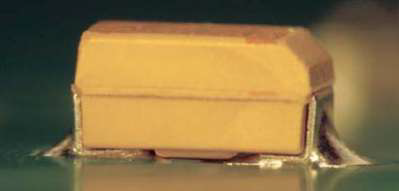

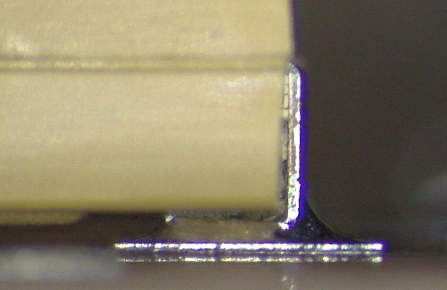

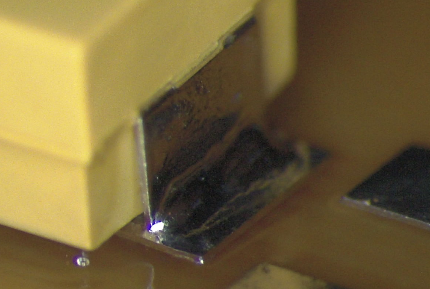

Rectangular and square end-capped or end-metallized component with rectangular body, leadless chip (see 10.4.2)

|

|

|

ceramic end capped chip resistors and capacitors. |

|

|

ceramic resistors arrays |

|

|

metallic terminations

|

|

|

metallic termination resistor

|

|

|

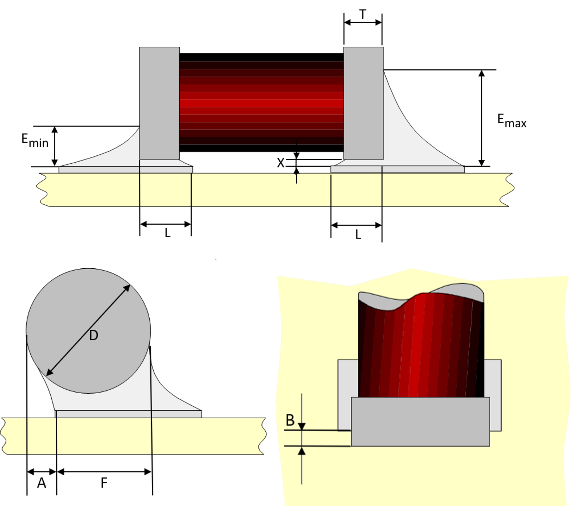

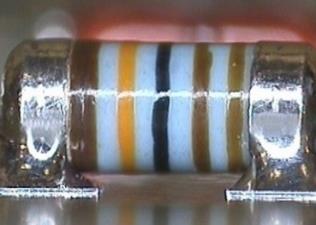

Cylindrical and square end-capped components with cylindrical or oval body, leadless chip (see 10.4.3)

|

|

|

MELF for cylindrical end capped:

|

|

|

Resistors in MELF, minimelf or micromelf

|

|

|

Square end capped:

|

|

|

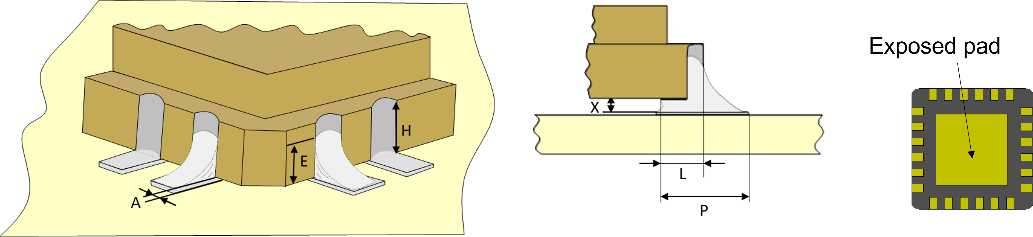

Bottom terminated chip component (see 10.4.4)

|

|

|

Chip inductors

|

|

|

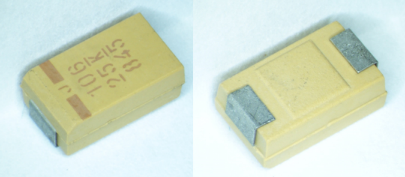

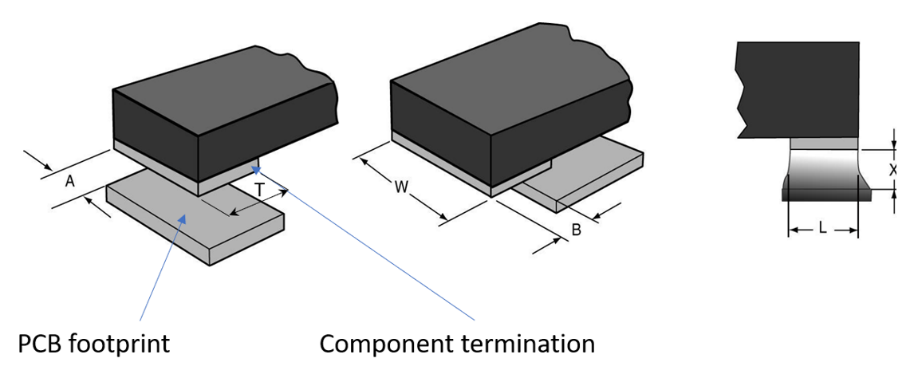

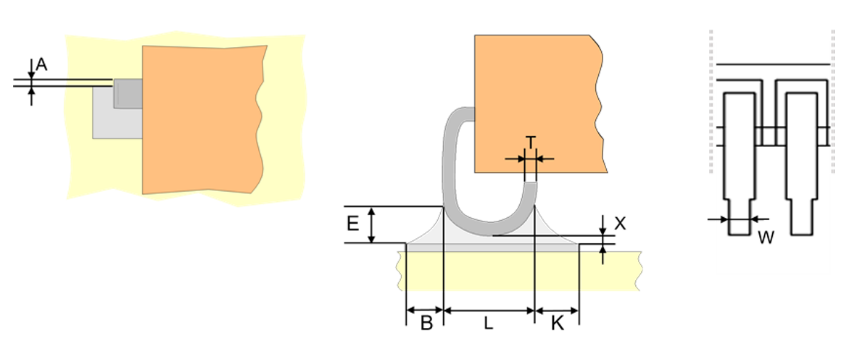

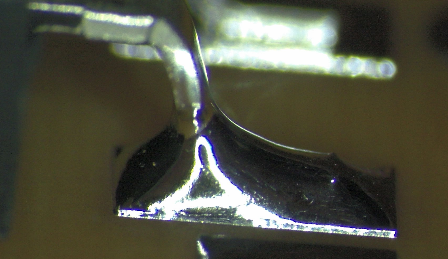

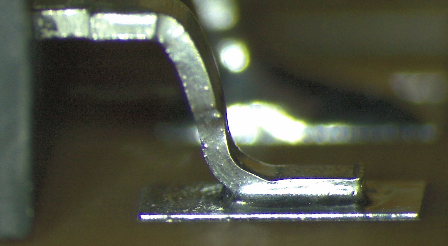

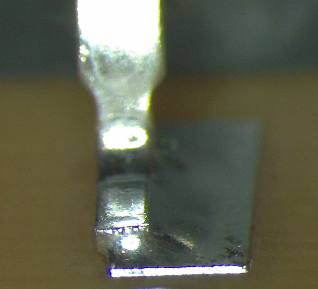

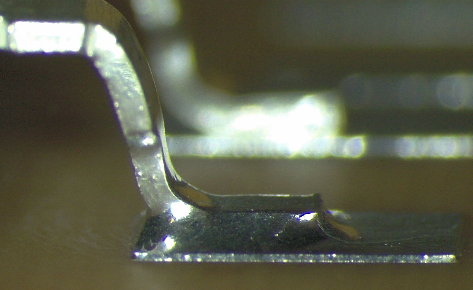

Component with inward formed L-shaped leads (see 10.4.5)

|

|

|

moulded tantalum chip capacitors. |

|

|

SMD moulded shunt

|

|

|

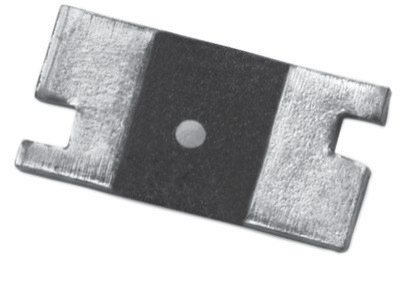

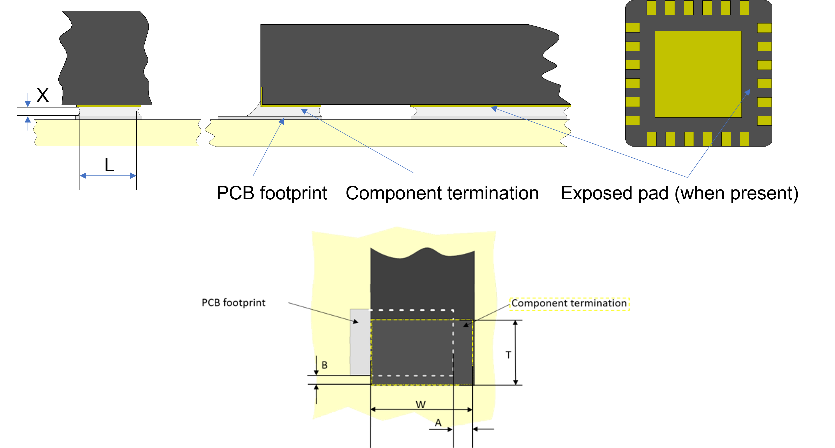

Leadless component with plane termination (see 10.4.6)

|

|

|

With metal plane termination: SMD0.5, SMD1, SMD2, SMD0.2*(TO276 JEDEC family denomination)

|

|

|

With non-metal plane termination: SMD0.2*

|

|

|

Leaded component with plane termination (see 10.4.7)

|

|

|

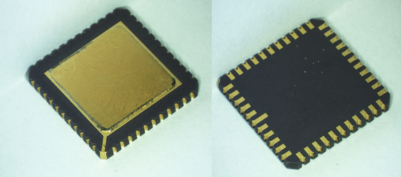

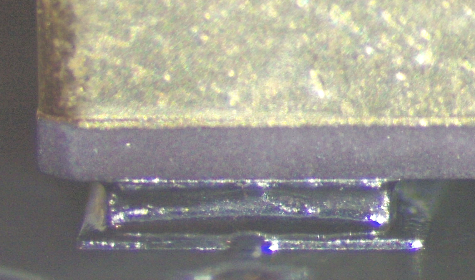

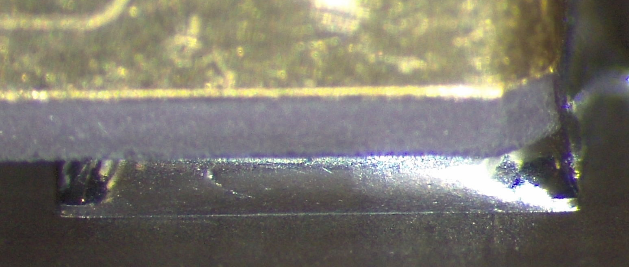

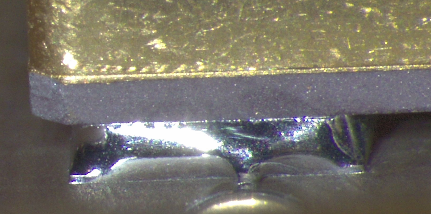

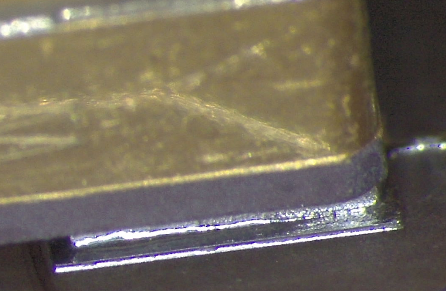

Leadless castellated ceramic chip carrier component (see 10.4.8)

|

|

|

The main component of this type is leadless ceramic chip carrier (LCCC) |

|

|

LCC6 |

|

|

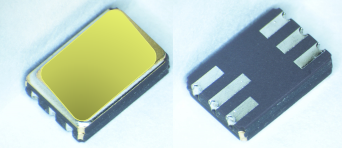

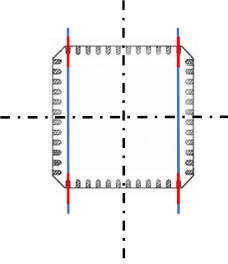

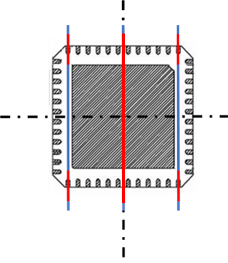

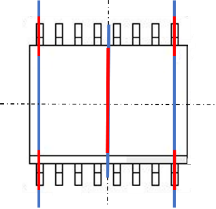

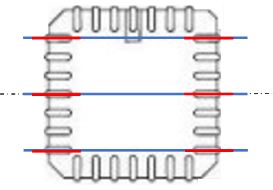

No lead QFN (see 10.4.9)

|

|

|

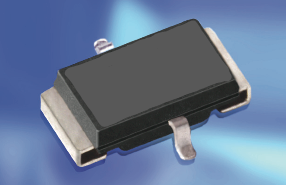

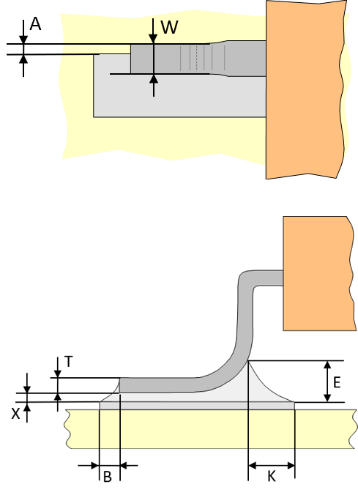

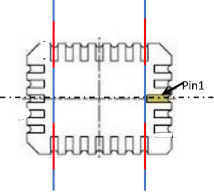

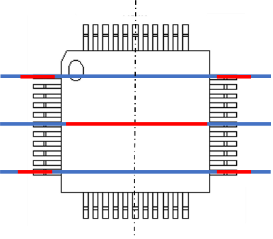

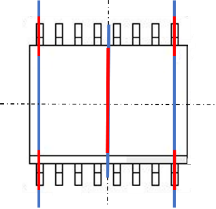

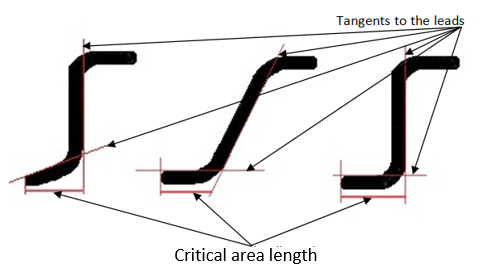

Flat pack and gull-wing leaded component (see 10.4.10)

|

|

|

small-outline transistor (SOT), small-outline package (SO), flat pack and quad flat pack (QFP) and SMD connectors with stress-relief (MHD).

|

|

|

transformers

|

|

|

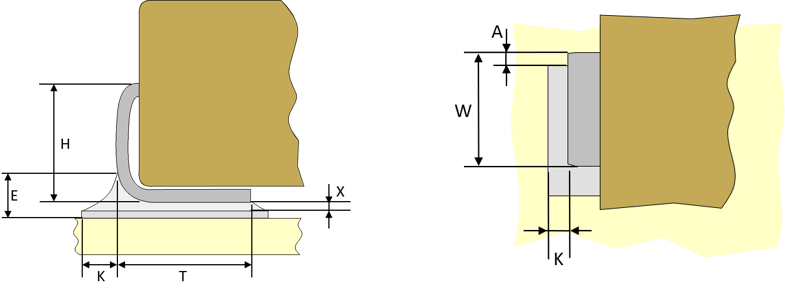

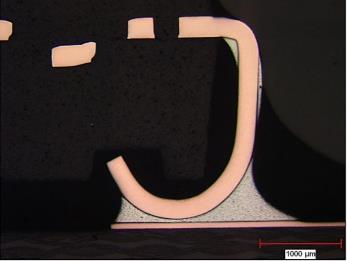

“J” leaded component

|

|

|

Components with ribbon terminals without stress relief (flat lug leads) (see 10.4.12)

|

|

|

Stacked modules components with leads protruding vertically from bottom (see 10.4.13)

|

|

|

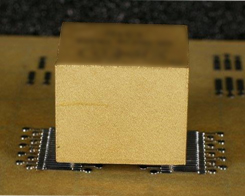

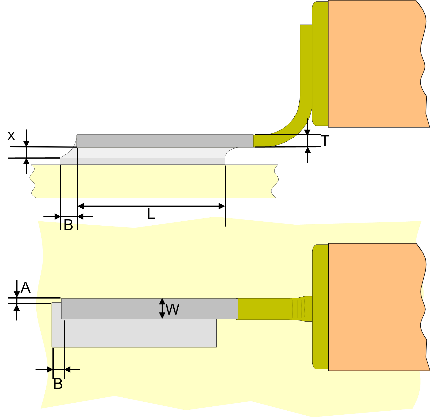

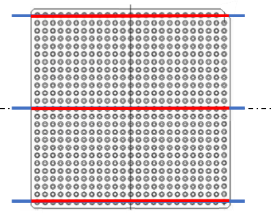

Area array components (AAD) (see 10.4.14)

|

|

|

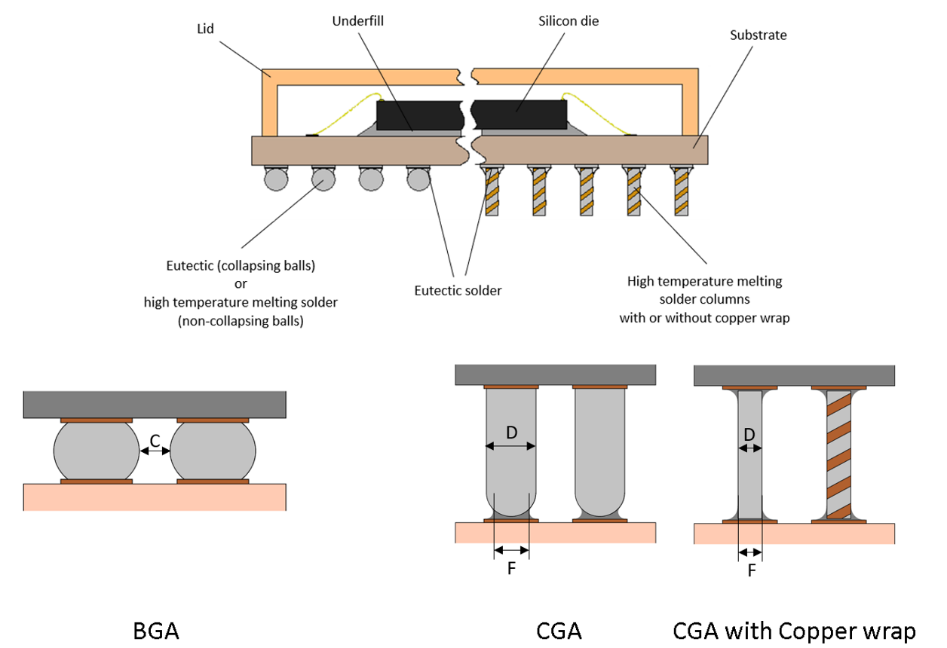

Solderless connection (see 10.7)

|

|

|

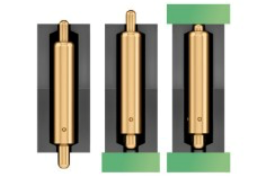

solderless interposers for LGA or connectors

|

|

Scope

This Standard defines the technical requirements and quality assurance provisions for the manufacture and verification of high-reliability electronic circuits of surface mount, through hole, solderless assemblies and soldering of harness and wire interconnection.

The Standard defines workmanship requirements, the acceptance and rejection criteria for high-reliability assemblies intended to withstand ground testing conditions including LTS (long term storage) and the environment imposed by space flight and launchers.

The mounting and supporting of components, terminals and conductors specified in this standard applies only to assemblies designed to continuously operate over the mission within the temperature limits of -55 °C to +85 °C at solder joint level.

Requirements related to printed circuit boards are contained in ECSS-Q-ST-70-60 and ECSS-Q-ST-70-12.

This standard does not cover lead-free soldering and associated requirements.

This Standard does not cover the qualification and acceptance of the EQM and FM equipment with high-reliability electronic circuits of surface mount, through hole and solderless assemblies.

This Standard does not cover verification of thermal properties for component assembly.

This Standard does not cover pressfit connectors due to the possible damage in the PCB that is not evaluated within this test requirement.

The qualification and acceptance tests of equipment manufactured in accordance with this Standard are covered by ECSS-E-ST-10-03.

This standard may be tailored for the specific characteristics and constraints of a space project, in accordance with ECSS-S-ST-00.

Normative references

The following normative documents contain provisions which, through reference in this text, constitute provisions of this ECSS Standard. For dated references, subsequent amendments to, or revision of any of these publications do not apply. However, parties to agreements based on this ECSS Standard are encouraged to investigate the possibility of applying the more recent editions of the normative documents indicated below. For undated references, the latest edition of the publication referred to applies.

|

ECSS-S-ST-00-01

|

ECSS system - Glossary of terms

|

|

ECSS-M-ST-40

|

Space project management - Configuration and information management

|

|

ECSS-Q-ST-10-09

|

Space product assurance - Nonconformance control system

|

|

ECSS-Q-ST-20

|

Space product assurance - Quality assurance

|

|

ECSS-Q-ST-60

|

Space product assurance - Electrical, electronic and electromechanical (EEE) components

|

|

ECSS-Q-ST-60-05

|

Space product assurance - Generic requirements for hybrids

|

|

ECSS-Q-ST-60-13

|

Space product assurance - Commercial electrical, electronic and electromechanical (EEE) components

|

|

ECSS-Q-ST-70

|

Space product assurance - Materials, mechanical parts and processes

|

|

ECSS-Q-ST-70-01

|

Space product assurance - Cleanliness and contamination control

|

|

ECSS-Q-ST-70-02

|

Space product assurance - Thermal vacuum outgassing test for the screening of space materials

|

|

ECSS-Q-ST-70-12

|

Space product assurance - Design rules for printed circuit boards

|

|

ECSS-Q-ST-70-28

|

Space product assurance - Repair and modification of printed circuit board assemblies for space use

|

|

ECSS-Q-ST-70-60

|

Space product assurance -Qualification and procurement of printed circuit boards

|

|

ECSS-Q-ST-70-71

|

Space product assurance -Materials processes and their data selection

|

|

ESA-STR-258

|

ESA-Approved Skills Certification Requirements

|

|

ESCC 23500 (September 2013)

|

Requirements for lead materials and finishes for components for space application

|

|

IPC J-STD-001H

|

Requirements for Soldered Electrical and Electronic

|

|

IPC J-STD-004B-AM1 (November 2011)

|

Requirements for Soldering Fluxes

|

|

IPC J -STD-033D (January 2018)

|

Handling, Packing, Shipping and Use of Moisture, Reflow, and Process Sensitive Devices

|

|

IPC-TM-650

|

Test methods manual. Surface Insulation Resistance, Fluxes

|

|

ISO 9454-1:2016

|

Soft soldering fluxes; classification and requirements

|

|

ISO 14644-1:2015

|

Cleanrooms and controlled environments

|

|

MIL-STD-883 K Method 2009 (April 2016)

|

Test Method Standard, Microcircuits

|

Terms, definitions and abbreviated terms

Terms from other standards

For the purpose of this Standard, the terms and definitions from ECSS-S-ST-00-01 apply.

For the purpose of this Standard, the terms and definitions from ECSS-Q-ST-60 apply, in particular for the following term(s):

commercial component

For the purpose of this Standard, the terms and definitions from ECSS-Q-ST-70-28 apply, in particular for the following term(s):

repair

rework

Terms specific to the present standard

Approval Authority

entity that reviews and accepts the verification programme, evaluating the test results and grants the final approval

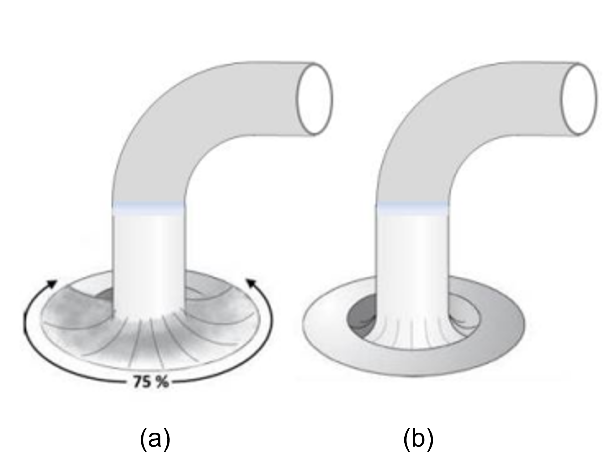

assembly sensitive component

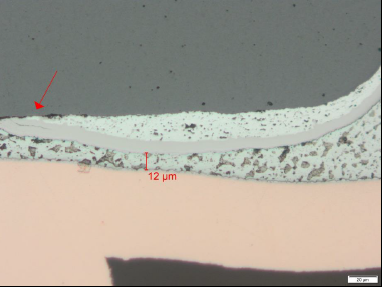

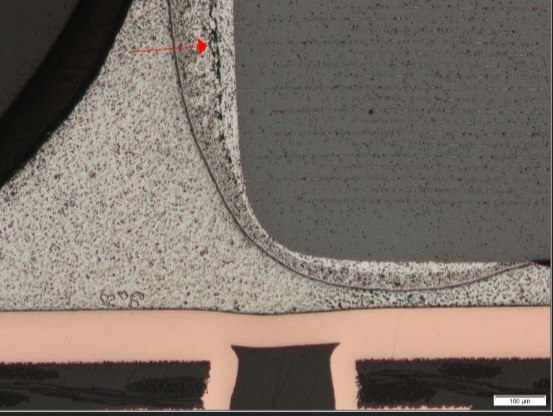

component prone to have cracks in solder joint exceeding 75 % of acceptance criteria of solder cracks or showing nonconformance outside the component manufacturer limit, due to assembly.

- 1 The ESA list of assembly sensitive components is regularly updated and published on ESCIES for information, see www.escies.org, Technologies - ESA SMT Verification. ESA-TECMSP-MO-018961.

- 2 Each company maintains its own list of assembly sensitive components in the PID.

bifurcated terminal

terminal containing a slot or split in which wires or leads are placed before soldering

The term "split terminal" is synonymous.

blister

delamination in form of localized swelling and separation between any of the layers of a laminated base material in a printed circuit board

bonding

application process of adhesive underneath a package for mechanical or thermal purpose

bridging

build-up of solder or conformal coating between components, component leads or base substrate forming an elevated path

clinched lead

conductor or component lead which passes through a printed circuit board and is then bent to contact the printed circuit board pad

The clinched portion is not forced to lie flat on the pad and some innate spring back is desirable before this form of termination is soldered.

cold flow

tendency of a solid material to move slowly or deform permanently under the influence of persistent mechanical stresses.

For example, for PTFE (Teflon) insulation sleeves under pressure.

cold solder joint

joint in which the solder has a blocky, wrinkled or piled-up appearance and shows signs of improper flow or wetting action

It can appear either shiny or dull, but not granular. The joint normally has abrupt lines of demarcation rather than a smooth, continuing fillet between the solder and the surfaces being joined. These lines are caused by either insufficient application of heat or the failure of an area of the surfaces being joined to reach soldering temperature.

conformal coating

thin polymeric film applied on a populated PCB that conforms to the shape of the surface it covers.

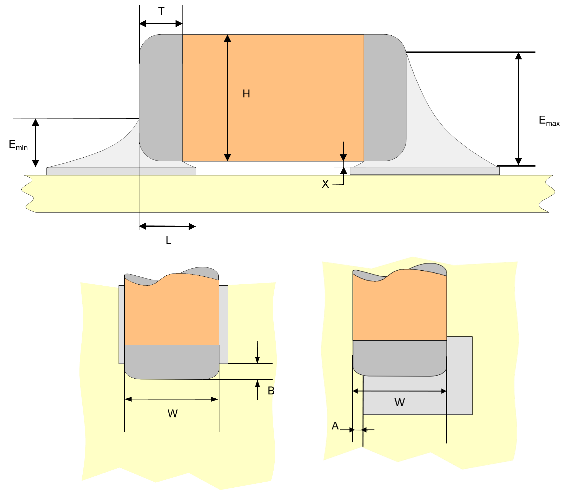

co-planarity

difference between maximum and minimum termination height when component rests on flat surface

collective assembled components

set of components that are soldered to PCB in one operation

For example, vapour phase soldered components, in contrast to manually soldered where each component is soldered individually.

critical zone

area in the solder joint in which the existence and magnitude of cracks is subject to acceptance or rejection

dewetting

condition in a soldered area in which the liquid solder has not adhered intimately, characterized by an abrupt boundary between solder and conductor, or solder and terminal/termination area

This is often seen as a dull surface with islands of thicker shiny solder.

disturbed solder joint

unsatisfactory connection resulting from relative motion between the conductor and termination during solidification of the solder

dynamic wave soldering machine

system that achieves wave soldering and which consists of stations for fluxing, preheating, and soldering by means of a conveyor

electrical clearance

spacing between separate electrical conductors of a printed circuit board assembly

exposed pad

exposed metallization on the bottom of a package

The exposed pad can have both electrical or thermal purpose and is often plated with same material and finish as the edge terminations, for soldering purposes. Exposed pad can be thermally bonded, soldered or left unconnected if not needed for the intended application.

fillet

smooth concave build-up of material between two surfaces

Example: A fillet of solder between a component lead and a solder pad or terminal, or a fillet of conformal coating material between a component and printed circuit board.

flux

material which, during soldering, removes the oxide film, protects the surface from oxidation, and permits the solder to wet the surfaces to be joined

glass meniscus

glass fillet of a lead seal which occurs where an external lead leaves the package body

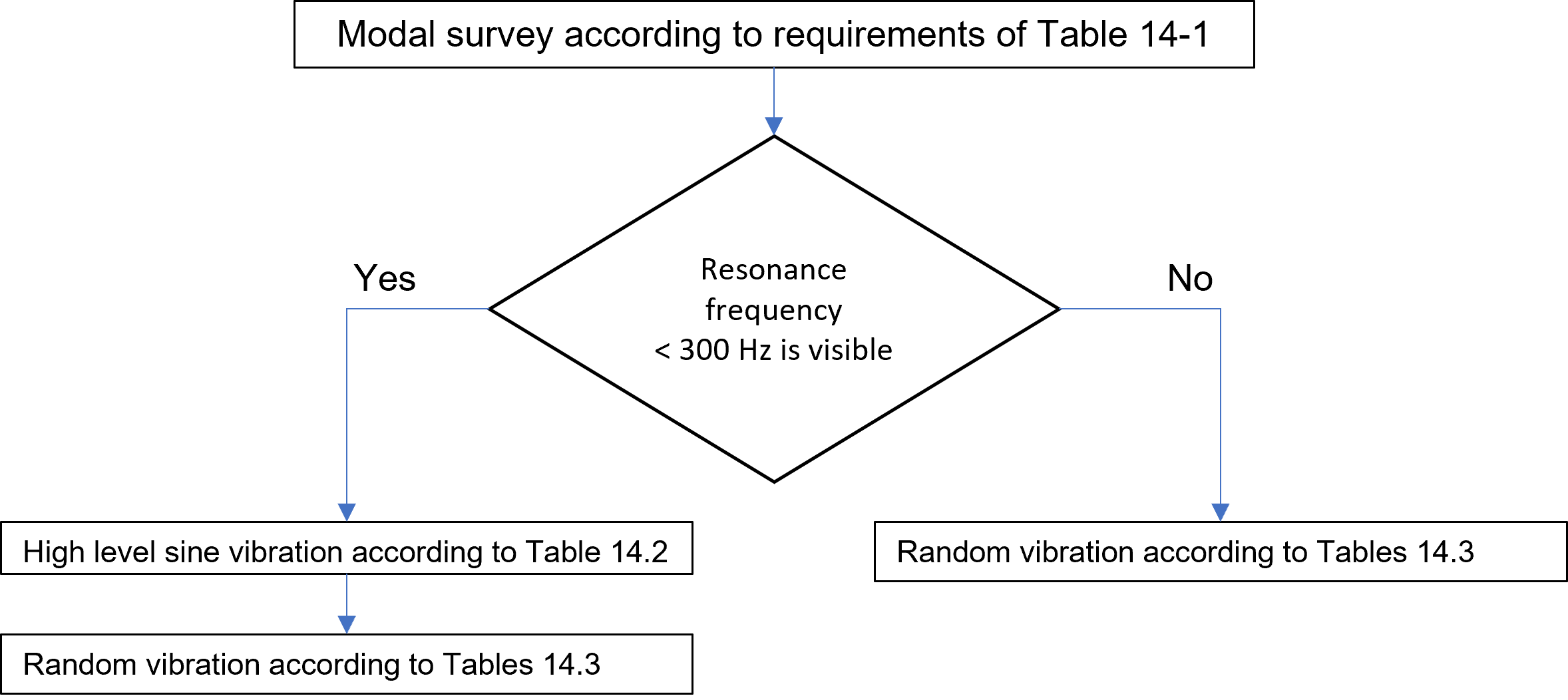

modal survey

characterization of the dynamic properties of systems in the frequency domain

A typical example is testing structures under vibrational excitation

outsourcing

act of subcontracting work to another company in compliance with customer PID

pin in paste

process where a through hole component is mounted and soldered in the surface mounting process

pits

small holes or sharp depressions in the surface of solder

This can be caused by flux blow-out due to entrapment or overheating.

potting compound

compound, usually electrically non-conductive, used to encapsulate or as a filler between components, conductors, or assemblies

pressfit connector

solderless termination technology where each contact is pressed into a plated hole of a printed circuit board creating a mechanical and electrical joint

reprocessing

preparatory operation done on a component prior to assembly

Degolding, pretinning, lead forming, and cutting are examples of reprocessing.

shield

metallic sheath surrounding one or more wires, cables, cable assemblies, or a combination of wires and cables that is used to prevent or reduce the transmission of electromagnetic energy to or from the enclosed conductors

The shield also includes an insulating jacket that can cover the metallic sheath.

solder balls

numerous spheres of solder having not melted in with the joint form and being scattered around the joint area normally attached by flux residues

Can be caused by incorrect preheating or poor-quality solder.

solder-cup terminal

hollow, cylindrical terminal closed at one end to accommodate one or more conductors

solder icicle

conical peak or sharp point of solder usually formed by the premature cooling and solidification of solder upon removal of the heat sources

solder pad

conductive surface on a printed circuit board to which terminations are soldered to form electrical connections

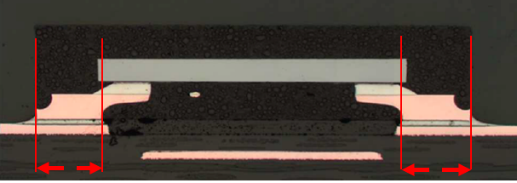

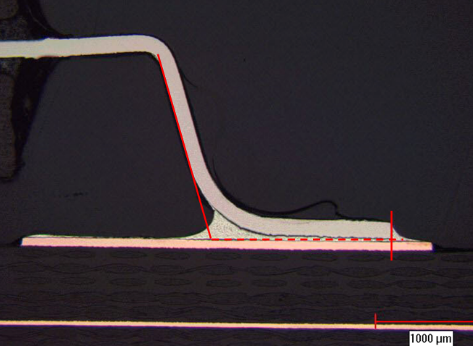

solder stand-off

thickness of solder between the underside of the component termination and the solder pad

split terminal

see "bifurcated terminal" 3.2.3

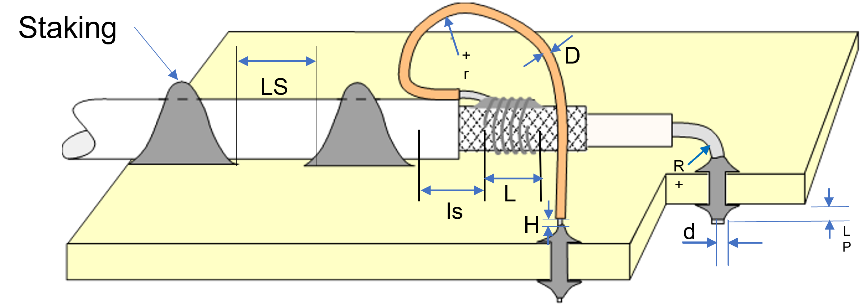

staking

application process of adhesive on the outside of a package for mechanical purpose

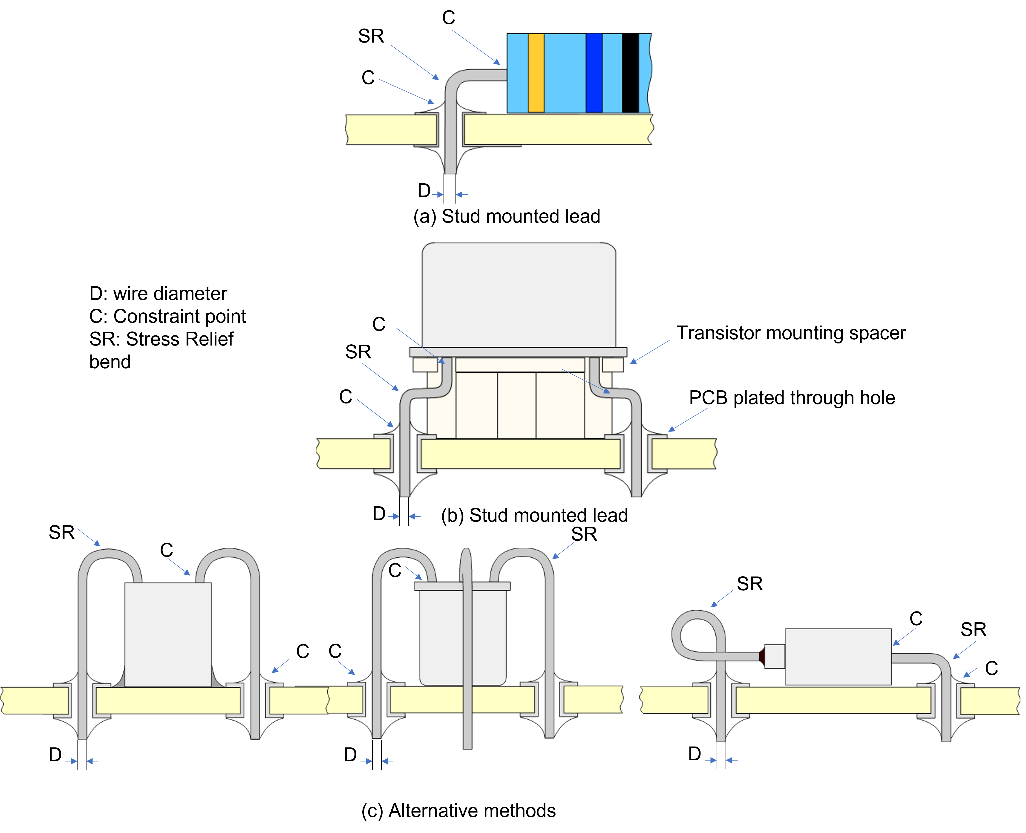

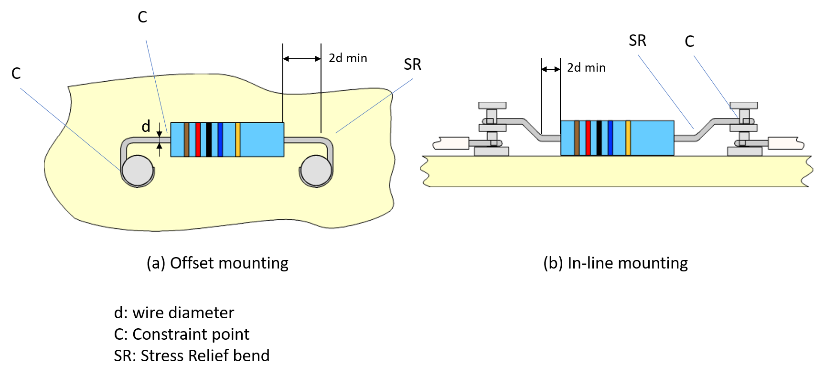

stress relief

method or means to minimize stresses to the soldered termination or component

Generally, in the form of a bend or service loop in a component lead, solid or stranded wire to provide relief from stress between terminations, as that caused, for instance by movement or thermal expansion.

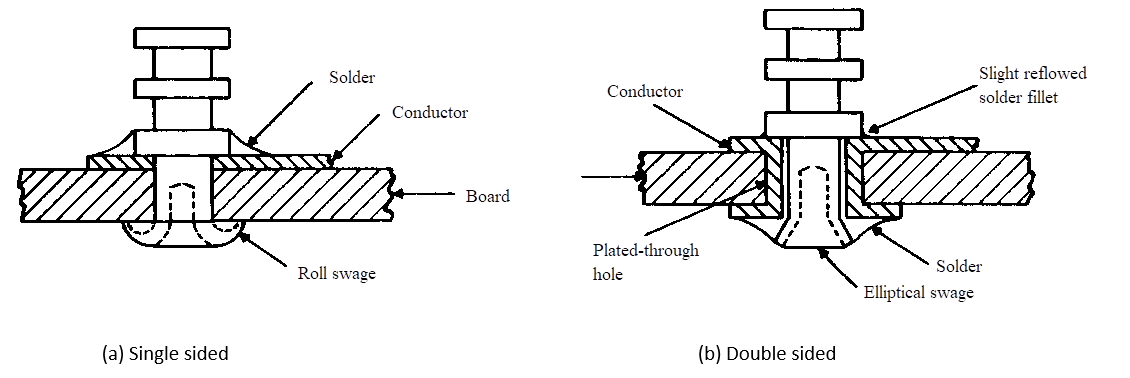

stud termination

upright conductor termination through a printed circuit board

technology samples

samples of boards assembled with representative technology

thermal shunt

element with good heat-dissipation characteristics used to conduct heat away from an article being soldered

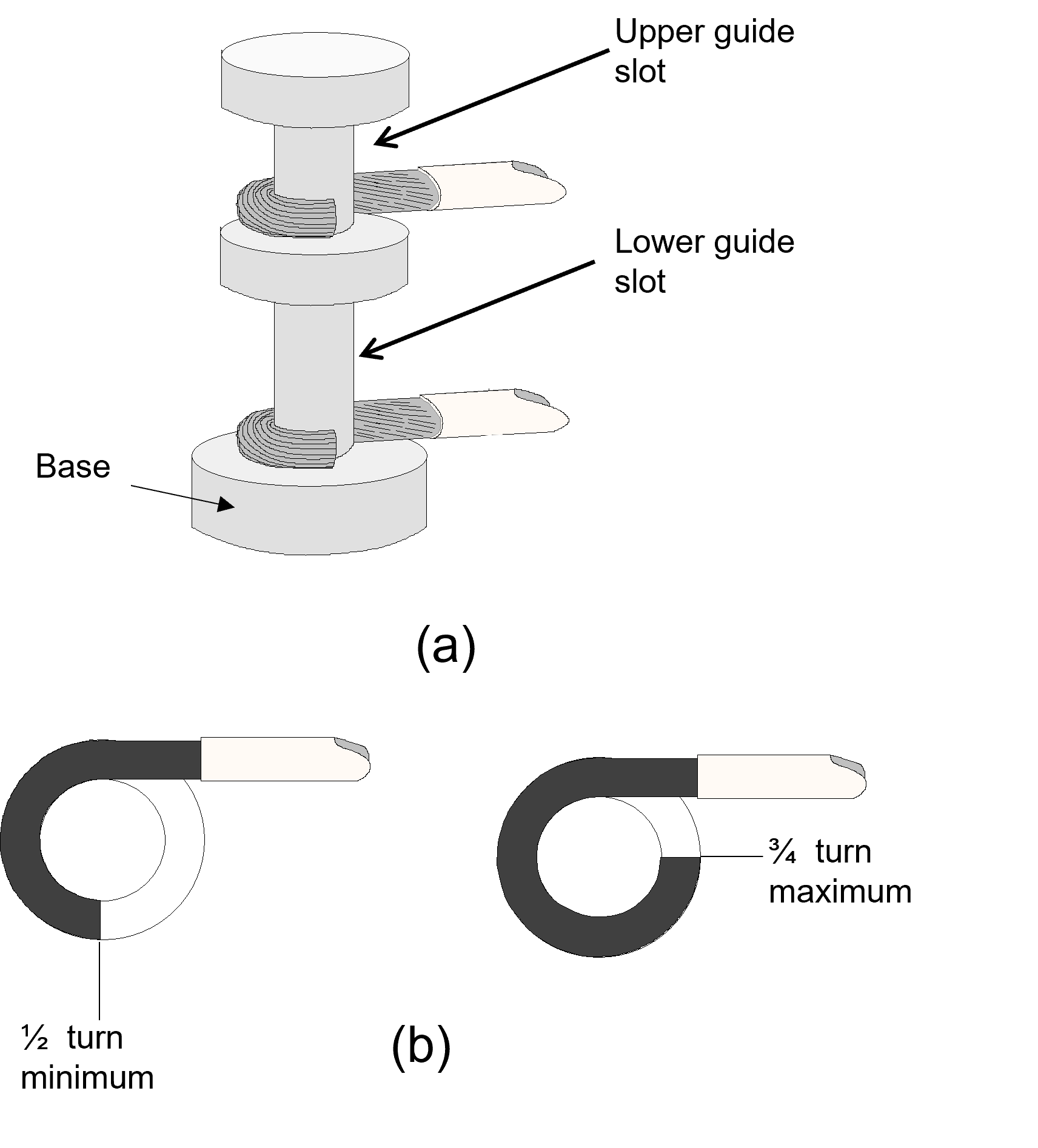

turret terminal

round post-type grooved stud around which conductors are fastened before soldering

underfill

material deposited between a component and substrate

verification board

substrate assembled with components subjected to a verification programme

wicking

flow of molten solder or cleaning solution by capillary action

Occurs when joining stranded wire; solder is drawn within the strands, but normally not visible on outer surface of strands. Wicking can also occur within the stress relief bend of a component lead.

Abbreviated terms

For the purpose of this Standard, the abbreviated terms from ECSS-S-ST-00-01 and the following apply:

|

Abbreviation

|

Meaning

| |

|

AAD

|

area array device

| |

|

AOI

|

automatic optical inspection

| |

|

AWG

|

American wire gauge

| |

|

AXI

|

automatic X-ray inspection

| |

|

BGA

|

ball grid array

| |

|

CBGA

|

ceramic ball grid array

| |

|

CCGA

|

ceramic column grid array

| |

|

CGA

|

column grid array

| |

|

CLCC

|

ceramic leadless chip carrier

| |

|

CTE

|

coefficient of thermal expansion

| |

|

DCL

|

declared component list

| |

|

DIL

|

dual in line

| |

|

DIP

|

dual in line package

| |

|

DPAK

|

diode package

| |

|

DRD

|

document requirement definition

| |

|

EDX

|

Energy dispersive X-ray

| |

|

ETFE

|

ethylene tetrafluoroethylene

| |

|

EPA

|

ESD protected area

| |

|

ESD

|

electrostatic discharge

| |

|

FEP

|

fluorinated ethylene propylene

| |

|

FM

|

flight model or flight hardware

| |

|

FP

|

flat pack package

| |

|

IST

|

interconnect stress testing

| |

|

JEDEC

|

Joint Electron Component Engineering Council

| |

|

LCCC

|

leadless ceramic chip carrier

| |

|

MELF

|

metal electrode face bonded

| |

|

MIP

|

mandatory inspection point

| |

|

MPCB

|

Materials, Mechanical Parts and Processes Control Board

| |

|

MRR

|

manufacturing readiness review

| |

|

MSL

|

moisture sensitivity level

| |

|

PCB

|

printed circuit board

| |

|

PLCC

|

plastic leaded chip carrier

| |

|

PID

|

process identification document

| |

|

PSD

|

power spectral density

| |

|

PTFE

|

polytetrafluoroethylene

| |

|

PTH

|

plated though hole

| |

|

QFN

|

quad flat pack no leads

| |

|

QFP

|

quad flat pack

| |

|

Rg

|

resistance to ground

| |

|

Rs

|

surface resistance

| |

|

r.m.s.

|

root-mean-square

| |

|

SEM

|

scanning electronic microscope

| |

|

SIR

|

surface insulation resistance

| |

|

SMD

|

surface mounted device

| |

|

SMT

|

surface-mount technology

| |

|

SO

|

small outline

| |

|

SOD

|

small outline diode

| |

|

SOT

|

small outline transistor

| |

|

SOP

|

small outline package

| |

|

TO

|

transistor outline

| |

|

TRB

|

test review board

| |

|

TRR

|

test readiness review

| |

|

TSOP

|

thin small outline package

| |

|

RF

|

radio frequency

| |

Nomenclature

The following nomenclature apply throughout this document:The word “shall” is used in this document to express requirements. All the requirements are expressed with the word “shall”.

The word “should” is used in this document to express recommendations. All the recommendations are expressed with the word “should”.

It is expected that, during tailoring, all the recommendations in this standard are either converted into requirements or tailored out.

The words “may” and “need not” are used in this document to express positive and negative permissions respectively. All the positive permissions are expressed with the word “may”. All the negative permissions are expressed with the words �“need not”.

The word “can” is used in this document to express capabilities or possibilities, and therefore, if not accompanied by one of the previous words, it implies descriptive text.

In ECSS “may” and “can” have a completely different meaning: “may” is normative (permission) and “can” is descriptive.

The present and past tense are used in this document to express statement of fact, and therefore they imply descriptive text.

Principles of reliable soldered connections

The following are the general principles to provide reliable soldered connections:

Reliable soldered connections are the result of proper design, control of tools, materials, processes work environments and workmanship performed in accordance to verified and approved procedures, inspection control and precautions.

The basic design concepts to provide reliable connections and to avoid solder joint failure are as follows:

Stress relief is an inherent part of the design which reduces detrimental thermal and mechanical stresses on the solder connections.

Where adequate stress relief is not possible materials are so selected that the mismatch of thermal expansion coefficients is a minimum at the constraint points in the component mounting configuration.

The assembled substrates are designed to allow easy inspection, rework, and repair.

The electrical and mechanical integrity of components and assemblies are retained after exposure to processes employed during manufacture and assembly, as handling, baking, fluxing, soldering, cleaning depanelization, electrical test and PCB integration.

Soldering to gold using tin-lead alloy can cause failure.

Preparatory conditions

Facility cleanliness

ECSS-Q-ST-70-61_1510001Personnel facilities shall be separated from the soldering areas.

Example: Washrooms, eating areas, smoking facilities.

ECSS-Q-ST-70-61_1510002Furniture shall be arranged to allow thorough cleaning of the floor and workbench.

ECSS-Q-ST-70-61_1510003Areas used for soldering shall be kept free from contaminants.

Loose material such as dirt, dust, solder particles, oil or clipped wires can contaminate soldered connections.

ECSS-Q-ST-70-61_1510004Working areas shall be kept free from any tools or equipment not used for the current task.

ECSS-Q-ST-70-61_1510005Working surfaces shall be covered with an easily cleaned hard top or have a replaceable surface of clean, non-corrosive, silicone-free ESD compatible paper.

ECSS-Q-ST-70-61_1510006Tools used during soldering operations shall be free of visible contaminant.

ECSS-Q-ST-70-61_1510007Excess lubricants shall be removed from tools before soldering starts.

Environmental conditions

ECSS-Q-ST-70-61_1510008The clean room shall be compliant to the requirements of clause 5.3.1 of ECSS-Q-ST-70-01.

ECSS-Q-ST-70-61_1510009The soldering area shall have as minimum a cleanliness level of ISO Class 8.2 in accordance with ISO 14644-1 (2015).

Particle concentrations for ISO Class 8.2 are not mentioned in the ISO Standard and can only be calculated with the formula in Annex E of ISO 14644-1 (2015). See Table 5-1.

Table 5-1: Particle concentrations classes 8 till 9 according to ISO 14644-1 (2015)

|

Particle sizes

| ||||

|

ISO class

|

0,5 µm

|

1 µm

|

5 µm

|

Comment

|

|

ISO-class 8

|

3 520 000 |

832 000 |

29 300 |

From Table 1 of ISO

|

|

ISO-class 8.1

|

4 430 000 |

1 050 000 |

36 800 |

Calculation acc ISO Annex E equation

|

|

ISO-class 8.2

|

5 570 000 |

1 320 000 |

46 400 |

Calculation acc ISO Annex E equation

|

|

ISO-class 8.5

|

11 100 000 |

2 630 000 |

92 500 |

From Annex E in ISO

|

|

ISO-class 9

|

35 200 000 |

8 320 000 |

293 000 |

From Table 1 of ISO

|

ECSS-Q-ST-70-61_1510010Areas used for assembly or cleaning of components and areas where toxic or volatile vapours are generated or released shall include a local air extraction system.

ECSS-Q-ST-70-61_1510011The room temperature of the facility shall be maintained at (22 ±3) C.

ECSS-Q-ST-70-61_1510012The relative humidity at room temperature of the facility shall be maintained at (55 ±10) %.

ECSS-Q-ST-70-61_1510013The soldering area shall not be exposed to draughts.

ECSS-Q-ST-70-61_1510014Air shall be supplied to the room through a filtering system that provides a positive pressure difference with respect to adjacent rooms.

Lighting requirements

ECSS-Q-ST-70-61_1510015Lighting intensity shall be a minimum of 1080 lux on the work surface.

In selecting a light source, the colour temperature of the light is an important consideration. Light ranges from 3000 K-5000 K enable users to distinguish various printed circuit assembly features and contaminants with increased clarity.

ECSS-Q-ST-70-61_1510016At least 90 % of the work area shall be without shadows or severe reflections.

Precautions against static discharges

Overview

Electronic components are particularly sensitive to electrostatic charging and discharging. To protect these components, it is necessary to define measures with regard to their handling, transport and storage.

The ESD control programme helps reducing to a minimum level the ESD-related damage to components. Main topics of the programme are:

ESD coordinator,

Training,

Product qualification,

Compliance verification,

Grounding/bonding systems,

Personnel grounding,

EPA requirements,

Packaging systems,

Marking.

The controls referenced in this document have been selected from document “ANSI/ESD S20.20-2014 2.0 SCOPE”. The goal is to prevent damage of the isolated conductors and of the ESD sensitive devices (ESDS) which are susceptible to discharges that are greater than or equal to 100 V (Human Body Model) or 200 V (Charged Device Model).

General

ECSS-Q-ST-70-61_1510017An ESD Control Programme in accordance with EN 61340-5-1 (2016) shall be developed and implemented by the supplier.

EN 61340-5-2 guideline can be used for editing the ESD Control Programme.

ECSS-Q-ST-70-61_1510018The process for the selection of new components shall include their ESD sensitivity.

ECSS-Q-ST-70-61_1510019Electrostatic sensitive components shall be handled, prepared, mounted, soldered, and cleaned in an ESD protected area compatible with ESD class of the components.

Electrostatic sensitive components are classified in different categories. For some, additional ESD conditions to the nominal are needed.

ESD Protected Area

ECSS-Q-ST-70-61_1510020ESD sensitive devices shall be assembled in an EPA.

ECSS-Q-ST-70-61_1510021As a minimum, a dissipative mat, a wrist strap and common grounding facility for both shall be in place in the EPA.

ECSS-Q-ST-70-61_1510022EPA areas shall be visibly marked as such.

ECSS-Q-ST-70-61_1510023ESD rules and regulations shall apply as specified in EN 61340-5-1 (2016).

ECSS-Q-ST-70-61_1510024If the measured electrostatic field or surface potential exceeds the stated limits, ionization or other charge mitigating techniques shall be used.

ECSS-Q-ST-70-61_1510025Relative Humidity shall be controlled in the EPA in accordance with requirement 5.2e.

Precautions against ESD during manufacturing

ECSS-Q-ST-70-61_1510026Delimited EPA and corresponding ESD control items shall be in compliance with Table 5-2.

ECSS-Q-ST-70-61_1510027Ionized air in presence of high voltage or RF shall be used in compliance with components manufacturer recommendations.

Static charges on isolated components or tooling can be dissipated using ionised air.

ECSS-Q-ST-70-61_1510028A wrist strap shall be worn by the operator.

ECSS-Q-ST-70-61_1510029Powered equipment at the workstation shall be grounded.

ECSS-Q-ST-70-61_1510030The normal value of the resistance between the tip of the soldering system and the ground of the ESD protected area shall not exceed 5 Ω.

The measurement is generally performed at soldering temperature.

ECSS-Q-ST-70-61_1510031A ground-fault circuit interrupter shall be installed.

ECSS-Q-ST-70-61_1510032Protective clothing shall be made from static dissipative material.

ECSS-Q-ST-70-61_1510033Gloves and finger cots shall be made from static dissipative material.

ECSS-Q-ST-70-61_1510034Tools, such as mounting aids, consumables, masking tape, shall be conductive or static dissipative.

ECSS-Q-ST-70-61_1510035Paperwork accompanying ESD sensitive components shall be contained in static dissipative bags or envelopes.

Example of accompanying paperwork are traveller logs, drawings, and instructions.

ECSS-Q-ST-70-61_1510036Paperwork shall not come into contact with ESD sensitive components.

ECSS-Q-ST-70-61_1510037Table 5-2: EPA requirements summary

|

ESD Control item

|

Limits values *

| |

|

Working surfaces, storage, racks and trolleys

|

Dissipative top surface

|

Rs <1 109

|

|

ESD protected to ground

|

Rg < 1109

| |

|

Flooring

|

ESD protected to ground

|

Rg < 1109

|

|

Ionization

|

|

Decay (1000 V to 100 V) in less than 20 s

|

|

Seating

|

ESD protected to ground

|

Rg <1109

|

|

Wrist strap system

|

ESD protected to ground

|

Rg <35 106

|

|

* Values are taken from Tables 2 and 3 of EN 61340-5-1:2016.

| ||

Protective packaging and ESD protection

ECSS-Q-ST-70-61_1510038All ESD-sensitive items shall be contained within ESD-protective containers for movement between and within ESD-protected areas.

ECSS-Q-ST-70-61_1510039ESD protective packaging shall display ESD warning signs.

ECSS-Q-ST-70-61_1510040If the packaging is not ESD safe, it shall be labelled accordingly.

The objective of ESD protection is to prevent ESD to the item contained within, to allow for dissipation of charge, and to prevent charging of the ESD item by an external electrostatic field.

ECSS-Q-ST-70-61_1510041A container providing mechanical and ESD protection shall be used, whenever the ESD-sensitive electronic assembly is transported within a manufacturing plant or during shipment to external destinations.

This can be achieved by a container with:

- an outer shell that provides adequate mechanical protection for the contents,

- foam or bubble wrap shock absorbing liners that have static shielding covers,

- shielding package for the ESD sensitive contents.

ECSS-Q-ST-70-61_1510042All static-shielding bags shall be metallized.

ECSS-Q-ST-70-61_1510043Bags, film, bubble wrap or foam of Pink-Polyethylene shall not be used near any ESD-sensitive item or within an ESD protected area.

Pink-polyethylene provides little protection against ESD events and voltage fields and is a contaminants source.

ECSS-Q-ST-70-61_1510044Shipping popcorn, foam liners and polystyrene foam shall not be used near ESD-sensitive items unless shielding overwrap protects them.

ECSS-Q-ST-70-61_1510045Electrostatic sensitive components shall be kept in appropriate ESD protected packaging.

For example, kept in shielded bags.

ECSS-Q-ST-70-61_1510046Containers for ESD sensitive components shall be labelled as such.

Equipment and tools

General

ECSS-Q-ST-70-61_1510047Equipment and tools shall be inspected to meet requirements from respective clauses 5.5.2 to 5.5.19.

ECSS-Q-ST-70-61_1510048All tools and inspection equipment shall be maintained and calibrated, and their results recorded in accordance with clause 17.

ECSS-Q-ST-70-61_1510049Equipment shall not generate, induce, or transmit electrostatic charges to components being placed.

ECSS-Q-ST-70-61_1510050Any machine or part of machine, in particular the conveyor, shall be grounded to avoid electrostatic discharge.

ECSS-Q-ST-70-61_1510051Machines and equipment used to solder surface mount components shall either be a type incorporating dynamic single or dual solder wave or be of the solder reflow type.

ECSS-Q-ST-70-61_1510052The supplier shall verify, based on the available documentation, that the equipment do not impose any processing parameters that are in contradiction to the processing parameters given by the individual component data sheets.

Examples of processing parameters include maximum temperature to avoid internal melting, thermal shocks, thermal damages, removal of marking ink, degradation of encapsulating plastic.

ECSS-Q-ST-70-61_1510053Temperature and time profiles for assembly shall be identified by the supplier and approved by the Approval Authority.

ECSS-Q-ST-70-61_1510054The supplier shall identify changes and implement a verification programme in compliance with the requirements from clause 13.

ECSS-Q-ST-70-61_1510055The supplier shall demonstrate the reproducibility of their processes.

Brushes

ECSS-Q-ST-70-61_1510056Medium-stiff natural- or synthetic bristle, ESD-safe, brushes shall be used for cleaning.

- 1 Special care has to be taken not to damage any surface or adjacent materials.

- 2 Brushes with wooden handle can be used.

ECSS-Q-ST-70-61_1510057Brushes shall be cleaned in a solvent in accordance with clause 6.4.

ECSS-Q-ST-70-61_1510058Brushes shall not be damaged by the solvents used for PCB cleaning.

ECSS-Q-ST-70-61_1510059Wire brushes shall not be used.

Cutters and pliers

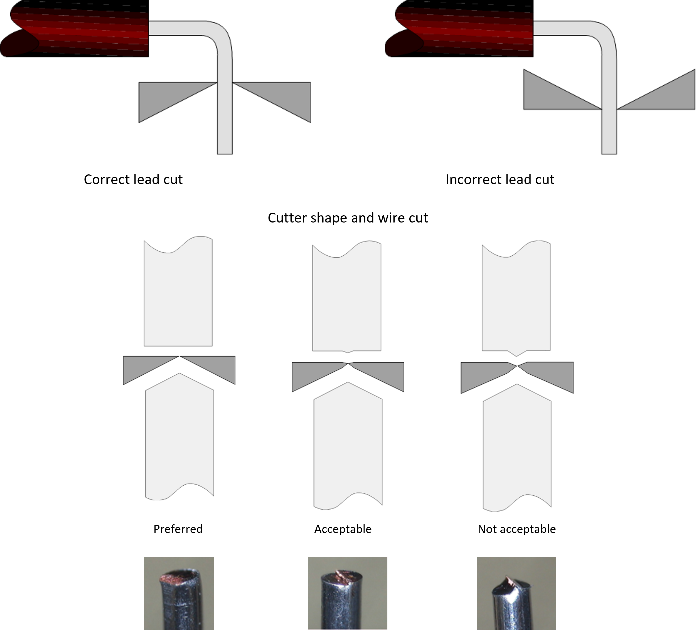

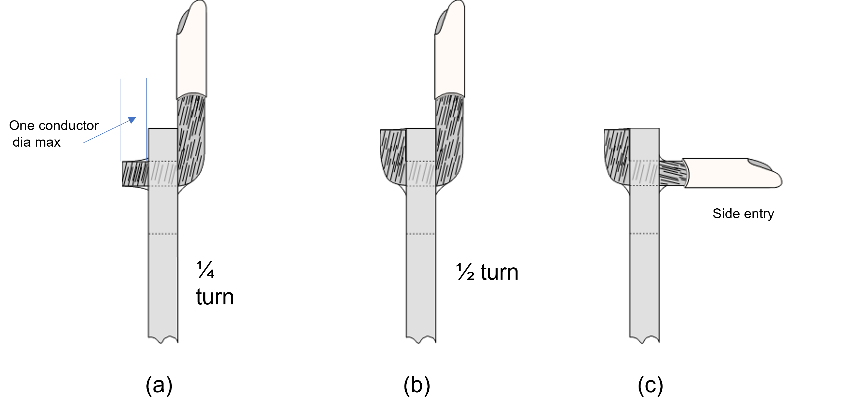

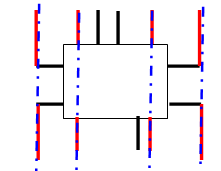

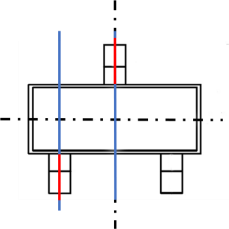

ECSS-Q-ST-70-61_1510060Cutting edge profiles and cutter usage shall be in accordance with Figure 5-1.

ECSS-Q-ST-70-61_1510061The cutter used for trimming conductor wire and component leads shall shear sharply, producing a clean, flat, smooth-cut surface along the entire cutting edge.

- 1 These measures minimize the transmission of mechanical and shock loads to delicate components.

- 2 Smooth, long-nose pliers or tweezers can be used for attaching or removing conductor wires and component leads.

ECSS-Q-ST-70-61_1510062No twisting action shall occur during the cutting operation.

ECSS-Q-ST-70-61_1510063Cutting edges shall be checked for damage and maintained in a sharp condition.

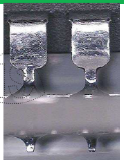

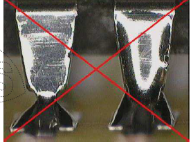

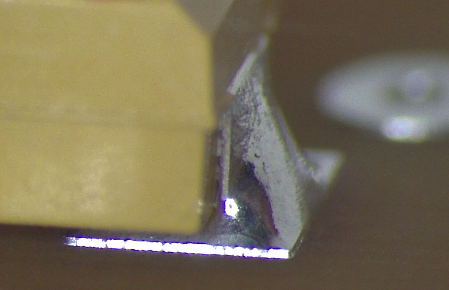

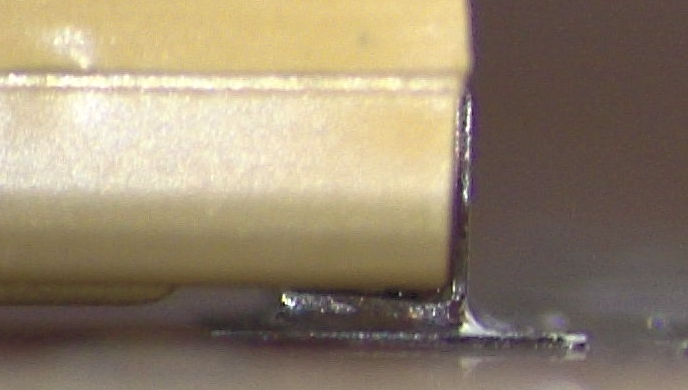

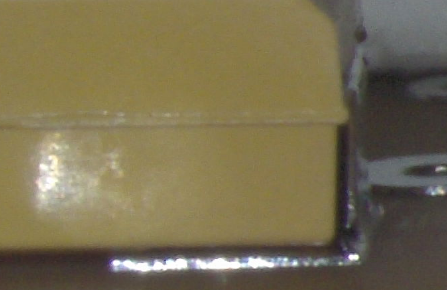

ECSS-Q-ST-70-61_1510064Figure 5-1: Profile of correct cutters for trimming leads

ECSS-Q-ST-70-61_1510064Figure 5-1: Profile of correct cutters for trimming leads

Bending tools

ECSS-Q-ST-70-61_1510065Component leads shall be bent or shaped using tools, including automatic bending tools, which do not nick or damage the leads or insulation.

ECSS-Q-ST-70-61_1510066Components shall not be damaged by the bending process specified in clause 8.2.7.

It is good practice to use bending tools with polished finish.

ECSS-Q-ST-70-61_1510067Bending tools shall have no sharp edges in contact with the component leads.

ECSS-Q-ST-70-61_1510068A maximum reduction of 10 % of initial section of the lead may be acceptable provided that it is representative of the verified configuration.

Clinching tools

ECSS-Q-ST-70-61_1510069Clinching tools shall not damage the surfaces of printed-circuit conductors, components or component leads.

Insulation strippers

Thermal strippers

ECSS-Q-ST-70-61_1510070The temperature of the stripper shall not burn, blister, or cause excessive melting of the insulation.

- 1 Thermal insulation strippers can be used for wire insulation types susceptible to damage by mechanical strippers.

- 2 It is good practice to apply thermal strippers for use with AWG 22 and smaller wire sizes where there is a possibility of the wire stretching if a mechanical stripper is used.

- 3 Local air extraction units can be used during thermal stripping.

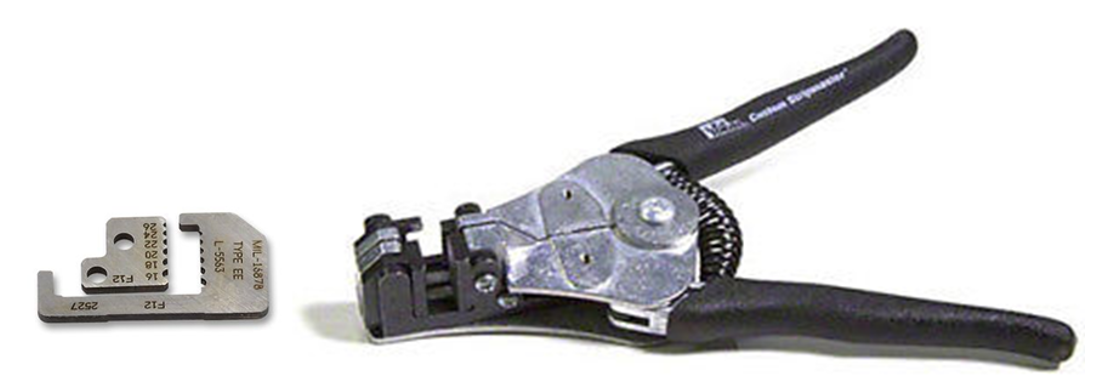

Precision mechanical cutting-type strippers

ECSS-Q-ST-70-61_1510071Mechanical strippers shall be of the following types:

- Automatic power-driven strippers with precision, factory-set, cutting, and stripping dies and wire guards, or

- Precision-type hand strippers with accurately machined and factory-pre-set cutting heads.

Figure 5-2 shows an example of acceptable mechanical strippers.

ECSS-Q-ST-70-61_1510072Stripping tools or machines shall fit the size of the wire conductor.

It is good practice to mask off the die openings for wire sizes not in use.

ECSS-Q-ST-70-61_1510073The conductor shall not be twisted, ringed, nicked, cut, or scratched by the process.

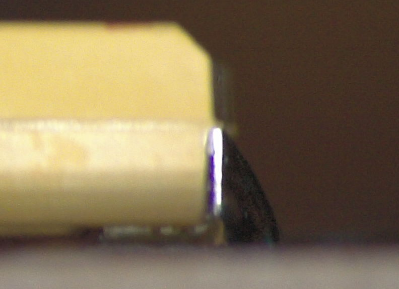

Figure 5-2: Example of suitable mechanical strippers

Figure 5-2: Example of suitable mechanical strippers

Enamel stripping for wires

ECSS-Q-ST-70-61_1510074The enamel shall be removed by chemical or thermal means.

ECSS-Q-ST-70-61_1510075The enamel may be removed by mechanical means provided that visual inspection using a minimum magnification of x40 is carried out to confirm absence of damage of the conductor.

ECSS-Q-ST-70-61_1510076When stripping the ends of enamel wires the complete removal of the enamel shall be verified by visual inspection.

ECSS-Q-ST-70-61_1510077Chemical stripping materials shall be completely neutralised and be cleaned such that there are no residues from the stripping, neutralizing, or cleaning steps.

ECSS-Q-ST-70-61_1510078The enamel shall not be visually contaminated by the stripping process.

Verification of stripping tools

ECSS-Q-ST-70-61_1510079Thermal and mechanical stripping tools shall be verified by removal of insulation at the start of each production batch.

Hot air blower

ECSS-Q-ST-70-61_1510080Hot air blower shall be used for shrinking of sleeves

ECSS-Q-ST-70-61_1510081Hot air blower may be used for removal of some adhesives

ECSS-Q-ST-70-61_1510082Hot air blower shall be able to maintain and control a defined temperature.

ECSS-Q-ST-70-61_1510083Temperature of the hot air blower shall be set at a temperature in compliance with the materials and not degrade surrounding assembly or materials.

it is good practice to have a thermocouple around to ensure absence of degradation.

ECSS-Q-ST-70-61_1510084Hot air blower shall meet requirement 5.5.1d against ESD.

Soldering tools

General

ECSS-Q-ST-70-61_1510085The leads shall not be damaged during preparation and assembly.

Holding tools

ECSS-Q-ST-70-61_1510086Holding tools used as soldering aids shall not be wetted by the solder during the assembly.

Thermal shunts

ECSS-Q-ST-70-61_1510087A thermal shunt shall be able to act as heat sink to protect thermally sensitive components.

- 1 An effective clamp-type thermal shunt can be constructed by inserting small copper bars into the jaws of an alligator clip.

- 2 Shunts can be held in place by friction, spring tension or any other means that does not damage the finish or insulation.

Anti-wicking tools

ECSS-Q-ST-70-61_1510088The conductor gauge sizes of the anti-wicking tools shall be marked on the tool.

Anti-wicking tools can be used for pretinning the stranded wires.

Soldering irons

ECSS-Q-ST-70-61_1510089The size and shape of the soldering iron and tip shall not damage adjacent areas or connections during soldering operations.

ECSS-Q-ST-70-61_1510090Temperature-controlled soldering irons shall be used.

ECSS-Q-ST-70-61_1510091Temperature of the solder tip shall be verified once a week and after each solder tip change.

ECSS-Q-ST-70-61_1510092Selected temperature of the solder tip shall remain within +/-10°C.

ECSS-Q-ST-70-61_1510093Resistance between the soldering tip and the workstation grounding point shall be compliant with IPC- J/STD/001H Sept 2020.

ECSS-Q-ST-70-61_1510094AC and DC current leakage from heated tip to ground shall not create deleterious effects on equipment or components.

ECSS-Q-ST-70-61_1510095Tip transient voltages generated by the soldering equipment shall not exceed 2 V peak under a minimum loading impedance of 100 kΩ.

ECSS-Q-ST-70-61_1510096A soldering iron holder shall be used.

It is good practice to use a cage-type holder that leaves the soldering-iron tip unsupported when a temperature-controlled soldering iron is used.

Baking and curing ovens

ECSS-Q-ST-70-61_1510097An oven for baking and curing shall be able to heat and maintain the temperature of a printed circuit board or assembly within ±10 °C.

- 1 It is good practice to take into account the size and number of objects to be heated, when selecting capacity and size of the oven.

- 2 A vacuum oven can be used for drying operation.

ECSS-Q-ST-70-61_1510098An oven used for silicone shall not be used to bake out PCBs.

ECSS-Q-ST-70-61_1510099An oven used for silicone shall not be used to cure adhesives other than silicone.

ECSS-Q-ST-70-61_1510100The oven shall be equipped with an independent automatic shutdown system to protect from overheating.

Solder deposition equipment

ECSS-Q-ST-70-61_1510101Equipment used to deposit solder pastes shall be of a screening, stencilling, dispensing, roller coating, dotting or jet printing type.

ECSS-Q-ST-70-61_1510102Solder deposit equipment shall deposit reproducible amount of solder paste.

The use of Solder Paste Inspection (SPI) equipment helps to ensure reproducible volume of deposited solder paste.

ECSS-Q-ST-70-61_1510103Equipment shall apply pastes of a viscosity and quantity such that the positioned component is retained on the board before and during soldering operations, ensuring self-centring and solder fillet formation.

ECSS-Q-ST-70-61_1510104Equipment used to apply solder preforms shall align the preform with the land or component lead and termination.

ECSS-Q-ST-70-61_1510105Solder paste deposition procedures and associated acceptance criteria shall be controlled and documented.

Automatic component placement equipment

ECSS-Q-ST-70-61_1510106Automatic or computer-controlled equipment used for component placement shall be of the coordinate-driven pick-and-place type or of the robotic type.

ECSS-Q-ST-70-61_1510107The placement equipment used shall be of a type that:

- prevents component or board damages,

- indexes components with respect to the circuit and

- aligns the component terminations with the board terminal areas.

Dynamic wave-solder machines

ECSS-Q-ST-70-61_1510108Dynamic soldering machines shall be of automatic type and of a design offering the following:

- Controlling the flux application.

- Controlling preheating to drive off volatile solvents and to avoid thermal shock damage to the PCB and component packages.

- Maintaining the solder temperature at the printed circuit board assembly to within ±5C of the established bath temperature throughout the duration of any continuous soldering run when measured 3,0 mm below the surface of the wave.

- Having a wave system that limits shadowing and allows solder fillet formation.

- Having carriers made from a material that cannot contaminate, degrade or damage the printed circuit board or substrate nor transmit vibration or shock stress from the conveyors to a degree permitting physical, functional or electrostatic damage to components, board or substrate during transport through preheating, soldering and cooling stages.

- Showing an extraction system, either integral or separate, conforming to the requirements of clause 5.2.

to item 4: It is good practice to use nitrogen atmosphere.

ECSS-Q-ST-70-61_1510109The following wave soldering machine parameters shall be controlled:

- the amount of flux and its coverage,

- the preheat temperature and duration to avoid damage to the PCB and to the component packages,

- the solder temperature so that the solder in the wave making contact with the board is 235 °C to 275 °C. ECSS-Q-ST-70-61_1510110The supplier shall provide evidence that:

- the conveyor speed does not vary by more than ±5 %, and

- the height of the solder wave remains to a constant preselected value across the width of the wave.

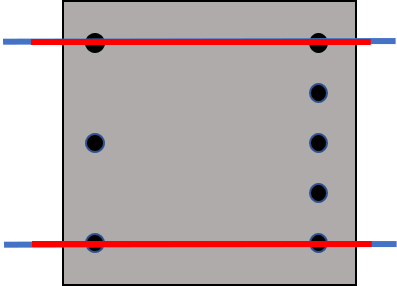

Selective wave solder equipment

ECSS-Q-ST-70-61_1510111Selective wave soldering machines shall be of automatic type and of a design offering the following:

- A holding mechanism for the board to be soldered, which can fixate the board during the process, without degrading or damaging the PCB or the mounted components.

- Nozzle, through which a local solder wave applies solder selectively per component or termination, from the solder side of the PCB to the component leads to be soldered.

- Automatic relative movement between nozzle and PCB both in-plane and out-of-plane direction.

- Controllable flux application.

- Maintain the preheating temperature to within 5 C during soldering to avoid thermal shock damage to the PCB and to component packages.

- Maintaining the wave solder temperature to within 5 °C of the established soldering temperature throughout the process.

- Showing an extraction system, either integral or separate, conforming to the requirements of clause 5.2.

to item 2: It is good practice to use local flow of nitrogen around the solder nozzle.

ECSS-Q-ST-70-61_1510112The following selective wave soldering machine parameters shall be controlled:

- the amount of flux and its coverage,

- the preheat temperature,

- the solder temperature so that the solder in the selective wave making contact with the board is maximum 300 °C,

- the nozzle speed so that the soldering time per lead does not exceed 10 s.

Reflow process equipment

Condensation (vapour phase) reflow machines

ECSS-Q-ST-70-61_1510113Condensation reflow machines shall:

- not transmit a movement or vibration into the assemblies being soldered that result in misalignment of components or disturbed solder joints,

- be capable of preheating an assembly with solder paste to the temperature recommended by the solder paste manufacturer prior to soldering,

- use a reflow fluid whose boiling point is a minimum of 17 C above the melting point of the solder being used,

- maintain the preselected temperature to within 5 C in the reflow zone during soldering,

- include an extraction system that conforms to clause 5.2.

to item 3: For boards with high thermal mass or for mixed terminations finish on components, it is a good practice to select a higher peak temperature and to use a delta of 30°C for a good wettability.

ECSS-Q-ST-70-61_1510114Reflow process parameters for condensation reflow machines shall be controlled and documented according to clause 5.5.14.5.

Local hot gas reflow machines

ECSS-Q-ST-70-61_1510115Local hot gas reflow machines shall:

- not transmit movement or vibration to the assemblies being soldered which result in misalignment of components or disturbed solder joints,

- preheat an assembly with solder paste to the temperature recommended by the solder paste manufacturer prior to soldering,

- heat the area of the assembly to be soldered using focused or unfocussed energy, to a preselected temperature that is a minimum of 30C above the melting point of the solder being used as measured at laminate or substrate surface,

- prevent the reflow of adjacent components and components localized on the opposite side,

- prevent excessive temperature that can degrade surrounding materials such as adhesive, underfill,

- Not to be above maximum allowed component temperature,

- maintain the preselected reflow temperature within 5C as measured at the substrate surface. ECSS-Q-ST-70-61_1510116Reflow process parameters for local hot gas reflow machines shall be controlled and documented according to clause 5.5.14.5.

Forced convection and infrared reflow systems

ECSS-Q-ST-70-61_1510117Forced convection and infrared reflow machines shall be of design such that the system:

- provides a controlled temperature profile and does not transmit movement or vibration into the assembly being soldered,

- preheats an assembly with solder paste to the temperature recommended by the solder paste manufacturer prior to soldering,

- heats the area of the assembly to be soldered using focused or unfocussed energy, to a preselected temperature that is a minimum of 30C above the melting point of the solder being used as measured at laminate or substrate surface,

- maintains the preselected temperature to within ±5 C in the reflow zone during soldering,

- not transmit movement or vibration to the assemblies being soldered which result in misalignment of components or disturbed solder joints. ECSS-Q-ST-70-61_1510118Reflow process parameters for forced convection and infrared reflow systems shall be controlled and documented according to clause 5.5.14.5.

Other equipment for reflow soldering

ECSS-Q-ST-70-61_1510119Other solder reflow systems may be approved for use by the Approval Authority under the condition that they meet the requirements of either clause 5.5.14.1, 5.5.14.2 or 5.5.14.3.

Reflow process control parameters

ECSS-Q-ST-70-61_1510120The following reflow process parameters shall be controlled and documented:

- preheat temperature to avoid damage to the PCB, to the component packages and to reduce the solder dwell time,

- solder reflow parameters and cooling parameters to stay inside the solder paste requirements,

- reflow temperature to be maintained within ±5 °C of the verified soldering temperature throughout the process,

- peak temperature is within the range of 200°C minimum and 235°C maximum, tolerances of point 3 included when measured at PCB level.

- capability to heat the soldering elements as PCB, components and to retain the present temperature within ±5 °C, and

- conveyor speed not to vary by more than ±5 %.

- 1 to item 3 and 4: It is good practice to use nitrogen if forced convection oven is used.

- 2 to item 1 and 6: It is good practice to apply a preheating rate of 2 °C ±0,5 °C/mn.

Depanelization tool

ECSS-Q-ST-70-61_1510121To prevent any damage on assembled PCB during depanelization, tools shall be able to meet following requirements:

- support PCBs to avoid bending and damage from vibration during process,

- guide cutting tool to avoid damage on PCB,

- use a local protection to avoid contamination,

- be a reproducible depanelization process.

Cleanliness testing equipment

ECSS-Q-ST-70-61_1510122Cleanliness testing equipment shall be able to:

- test the cleanliness of bare and assembled printed circuit boards,

- be sensitive enough to fulfil requirement 11.1.4e.2,

- meet the requirements of IPC-TM-650 Method 2.3.25.

Optical microscope

ECSS-Q-ST-70-61_1510123Optical microscope used for visual inspection shall provide optical magnification from 4x to 40x.

ECSS-Q-ST-70-61_1510124Optical microscope used for failure analysis shall provide, in addition to requirement 5.5.17a, an optical magnification from 50x to 500x.

Automatic Optical Inspection (AOI) equipment

ECSS-Q-ST-70-61_1510125AOI shall not replace final visual inspection.

AOI is an aid for inspection.

ECSS-Q-ST-70-61_1510126AOI equipment should be capable of detecting the following defects:

- Missing component

- Wrong type of component

- Wrong polarization

- Component upside down

- Misplacement

- Tombstoning or component placed on its edge

- Solder bridging

- Lack of solder

- Shape of solder joint when using a 3D AOI equipment.

X-ray inspection equipment

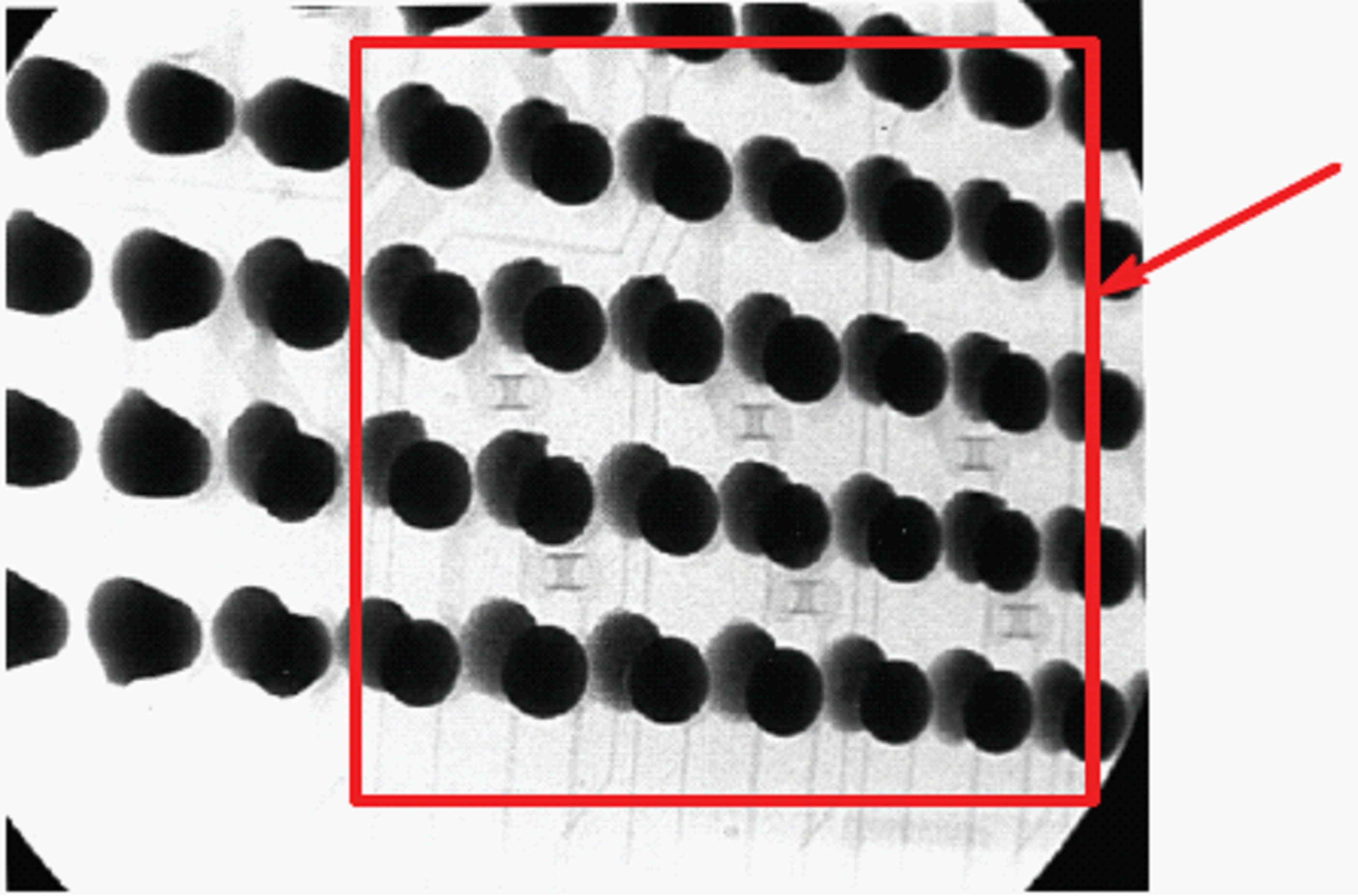

ECSS-Q-ST-70-61_1510127X-ray equipment shall be equipped with the following:

- X-ray tube with an acceleration voltage that permitted to provide the required resolution,

- X-ray tube with micro-focus technology,

- a digital detector with high resolution, and

- a system with variable expansion factor.

X-ray equipment not intended for electronic assemblies or not properly set up can damage sensitive components.

ECSS-Q-ST-70-61_1510128X-ray equipment shall be calibrated to evaluate the total dose received by the components during the inspection.

To minimize the dose given to the component, it is good practice to:

- Record the total dose received.

- Use off-line image analysis as much as possible.

- Use filters, optimizing the direction of the X-ray beam and masking sensitive areas.

ECSS-Q-ST-70-61_1510129The resolution of the X-ray equipment shall be able to detect solder balls having a diameter of 0,03 mm.

ECSS-Q-ST-70-61_1510130The sensitivity shall be demonstrated by means of actual 0,03 mm diameter solder balls, stuck to adhesive tape, attached to the multilayer board assembly being inspected.

ECSS-Q-ST-70-61_1510131AXI (Automatic X-ray inspection) shall not replace final visual inspection.

AXI can be used for inline inspection.

ECSS-Q-ST-70-61_1510132AXI equipment should be capable of detecting the following defects:

- Missing component

- Component upside down

- Misplacement

- Tombstoning or component placed on its edge

- Solder bridging

- Lack of solder.

Material selection

General

ECSS-Q-ST-70-61_1510133Material selection shall be in accordance with the requirements of ECSS-Q-ST-70 and ECSS-Q-ST-70-71.

ECSS-Q-ST-70-61_1510134All materials remaining on the assembled board shall be specified in the bill of materials.

ECSS-Q-ST-70-61_1510135Electronic components, mechanical components, printed boards, selected for assembly shall be compatible with all materials and processes, temperature ratings, used to assemble the product.

ECSS-Q-ST-70-61_1510136External finishes of components, subassemblies, assemblies, and hardware for space flight application shall have minimum 3 % Lead in case of tin/lead finish.

ECSS-Q-ST-70-61_1510137Electrical and electronic components identified as having plated or metallized external surfaces with a tin finish containing more than 97 % tin shall be pretinned with a tin-lead solder in accordance with clause 7.6.

Tin whisker mitigation (barrier methods such as coating or sleeving) is addressed in the framework of an NRB or to the Approval Authority.

ECSS-Q-ST-70-61_1510138Limited shelf-life items shall be handled and stored in accordance with ECSS-Q-ST-70-22 and in accordance with the material manufacturer’s recommendations.

Solder

Form

ECSS-Q-ST-70-61_1510139For soldering, solder paste, ribbon, wire and preforms shall be used provided that the alloy and flux meet the requirements of this standard.

ECSS-Q-ST-70-61_1510140Alloy for use in solder baths, for degolding, pretinning and wave soldering, shall be supplied without flux and be compliant with the requirements of Table 6-1.

Bars and ingots are example of procured alloys.

Composition

ECSS-Q-ST-70-61_1510141The solder alloy shall have a composition specified in Table 6-1.

- 1 Complementary information can be found in EN-IEC 61190-1-3 for solder and EN-IEC 61190-1-2 for solder paste.

- 2 The solder alloy used depends upon the application. See Annex H for guidelines for the choice of solder type.

ECSS-Q-ST-70-61_1510142In case of use of any solder not listed in Table 6-1, a verification shall be performed in compliance with clause 13.

ECSS-Q-ST-70-61_1510143The metal purity of solder shall be as specified in Table 6-1.

ECSS-Q-ST-70-61_1510144Table 6-1: Chemical composition of spacecraft solders

|

ESA

|

Sn

|

Pb

|

In

|

Sb

|

Ag

|

Bi

|

Cu

|

Fe

|

Zn

|

Al

|

As

|

Cd

|

Other

|

|

min % - max %

|

max %

|

min % - max %

|

max %

|

min % - max %

|

max %

|

max %

|

max %

|

max %

|

max %

|

max %

|

max %

|

max %

| |

|

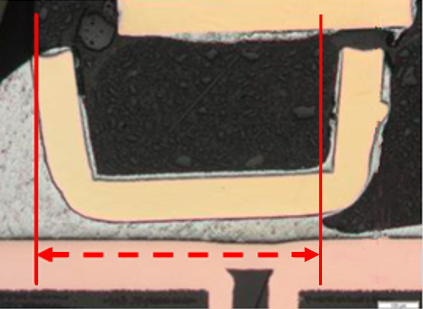

PTH and SMD assembly applications

| |||||||||||||

|

63 Tin solder

|

62,5-63,5

|

remainder

|

-

|

0,05

|

-

|

0,10

|

0,05

|

0,02

|

0,001

|

0,001

|

0,03

|

0,002

|

0,08

|

|

62 Tin Silver loaded

|

61,5-62,5

|

remainder

|

-

|

0,05

|

1,8-2,2

|

0,10

|

0,05

|

0,02

|

0,001

|

0,001

|

0,03

|

0,002

|

0,08

|

|

60 Tin solder

|

59,5-61,5

|

remainder

|

-

|

0,05

|

-

|

0,10

|

0,05

|

0,02

|

0,001

|

0,001

|

0,03

|

0,002

|

0,08

|

|

Only PTH assembly applications

| |||||||||||||

|

96 Tin solder

|

remain

|

0,10

|

-

|

0,05

|

3,5-4,0

|

0,10

|

0,05

|

0,02

|

0,001

|

0,001

|

0,03

|

0,002

|

0,08

|

|

Only for SMD assembly applications

| |||||||||||||

|

75 Indium Lead

|

max 0,25

|

remainder

|

74,0-76,0

|

0,05

|

-

|

0,10

|

0,05

|

0,02

|

0,001

|

0,001

|

0,03

|

0,002

|

0,08

|

|

70 Indium Lead

|

0,00-0,10

|

remainder

|

69,3-70,7

|

0,05

|

-

|

0,10

|

0,05

|

0,02

|

0,001

|

0,001

|

0,03

|

0,002

|

0,08

|

|

50 Indium Lead

|

0,00-0,10

|

remainder

|

49,5-50,5

|

0,05

|

-

|

0,10

|

0,05

|

0,02

|

0,001

|

0,001

|

0,03

|

0,002

|

0,08

|

|

(*): can be for PTH applications providing successful assembly verification

| |||||||||||||

Storage and handling of paste purity

ECSS-Q-ST-70-61_1510145Manufacturers’ instructions shall be applied for the handling and storage of containers of solder paste purchased premixed.

ECSS-Q-ST-70-61_1510146Refrigerated solder paste shall reach room temperature before opening the container.

ECSS-Q-ST-70-61_1510147Purchased premixed paste shall not be used if the use-by date or shelf life recommended by the manufacturer of the paste or paste constituents has expired.

ECSS-Q-ST-70-61_1510148When relifing is performed on purchased premixed paste, and it passes the specified tests, the relifing shelf life shall be half the initial shelf life according to ECSS-Q-ST-70-22 clause 4.1.4

As an example, for solder paste, solder ball test and viscosity can be part of relifing.

ECSS-Q-ST-70-61_1510149Tools used for removing solder paste from the container shall not contaminate the paste dispensed or that remaining within.

Fluxes

Rosin based fluxes

ECSS-Q-ST-70-61_1510150Fluxes shall be selected in accordance with Table 6-2.

- 1 Complementary information for fluxes can be found in ISO 9454-1:2016.

- 2 Flux manufacturers are mainly in compliance with IPC J-STD-004B-AM1 (2011).

ECSS-Q-ST-70-61_1510151For soldering the following fluxes shall be selected: - As a baseline, use ROL0 pure rosin flux.

- When ROL1 flux is used, monitor the effectiveness of subsequent cleaning operations in accordance with clause 11.1.2. ECSS-Q-ST-70-61_1510152High activated rosin-based fluxes shall be stored separately from pure rosin fluxes and low activated rosin fluxes.

Example: High activated rosin flux ROH1.

ECSS-Q-ST-70-61_1510153Table 6-2: Fluxes

|

|

IPC J-STD-004B-AM1 (2011) designation

|

Equivalent designation from ISO 9454-1:2016

|

Nature

|

Max composition* (Weight %)

|

|

Pretinning

| ||||

|

Normal wetting

|

ROL0

|

1111

|

Rosin

|

< 0,05 % halide

|

|

ROL1

|

1122

|

Rosin

|

< 0,5 % halide

| |

|

Difficult wetting

|

ROM1

|

1123

|

Rosin

|

0,5 % - 2 % halides

|

|

Difficult wetting

|

ROH1

|

1124

|

Rosin

|

2,0 % halides

|

|

Soldering

| ||||

|

Preferred

|

ROL0

|

1111

|

Rosin

|

< 0,05 % halide

|

|

Requiring cleanliness testing

|

ROL1

|

1122

|

Rosin

|

< 0,5 % halide

|

|

* Maximum values of halide contents are based on IPC, which have higher limits than ISO

| ||||

Solvents

ECSS-Q-ST-70-61_1510154Solvents for the removal of grease, oil, dirt, flux, and flux residues shall be electrically non-conductive and non-corrosive.

ECSS-Q-ST-70-61_1510155Solvents shall be efficient such that flux residues are removed according to clause 11.1.2.

ECSS-Q-ST-70-61_1510156Solvents shall not dissolve or degrade the quality of components or materials.

ECSS-Q-ST-70-61_1510157Solvents shall not remove component identification markings.

ECSS-Q-ST-70-61_1510158Containers of solvents shall be labelled.

ECSS-Q-ST-70-61_1510159Solvents shall be maintained in an uncontaminated condition.

ECSS-Q-ST-70-61_1510160Solvents showing visual evidence of contaminants or decomposition shall not be used.

ECSS-Q-ST-70-61_1510161The following solvents shall be used for cleaning in soldering operations:

- ethyl alcohol, 99,5 % pure by weight or 95 % pure by volume,

- isopropyl alcohol, 99 % pure,

- deionized water at a maximum temperature of 40 C is used for removing certain fluxes provided that the assembly is thoroughly dried directly after cleaning,

- any mixture of 6.4h.1, 6.4h.2 and 6.4h.3.

ECSS-Q-ST-70-61_1510162Other solvents that pass a compatibility test programme agreed by the Approval Authority may be used.

ECSS-Q-ST-70-61_1510163Solvents shall be selected such that they dry completely.

Flexible insulation materials

ECSS-Q-ST-70-61_1510164Materials shall have low outgassing properties in accordance with clause 5.5 of ECSS-Q-ST-70-02.

ECSS-Q-ST-70-61_1510165The following flexible insulation materials may be used in a space environment:

- ETFE, FEP and PTFE.

- Polyolefin and PVDF (Kynar®) sleeving for heat-shrinkable wire terminations.

- Irradiated polyethylene, fluorinated resin, and polyimide.

Terminals

Materials

ECSS-Q-ST-70-61_1510166Terminals shall be made from one of the following materials:

- Bronze (copper-tin) alloys.

- Brass (copper-zinc) alloys.

It is good practice to use bronze terminals.

ECSS-Q-ST-70-61_1510167When a brass terminal is used it shall be plated with a barrier layer of copper or nickel of 3 µm to 10 µm.

- 1 A barrier layer is necessary on brass items to prevent the diffusion, and subsequent surface oxidation, of zinc.

- 2 It is good practice to use a copper barrier layer on brass terminals because nickel is magnetic Terminals shall be tin lead plated with an alloy containing a minimum of 3 % Lead.

Example: Hot-dipped or reflowed electro-deposited plating.

Tin, silver, and gold-plated terminals

ECSS-Q-ST-70-61_1510168Terminals with pure tin, silver or gold-plated finish shall not be soldered to PCB.

ECSS-Q-ST-70-61_1510169Gold-plated finishes shall be replaced using one of the methods described in clause 7.6.

ECSS-Q-ST-70-61_1510170The maximum gold thickness of the terminal shall be specified in the procurement specification.

ECSS-Q-ST-70-61_1510171Pure tin and silver finishes shall be pretinned according to clause 7.6.4.

Wires

ECSS-Q-ST-70-61_1510172Wire shall be made from high-purity copper or copper alloy.

ECSS-Q-ST-70-61_1510173The wire shall have one of the following finishes:

- Silver-plating of a minimum 2 µm thickness,

- Wire-drawn, fused pure tin,

- Enamelled.

ECSS-Q-ST-70-61_1510174Wires shall be stripped of their insulation in accordance with clause 7.5.1.

ECSS-Q-ST-70-61_1510175Wires shall be pretinned in accordance with clause 7.6.4.

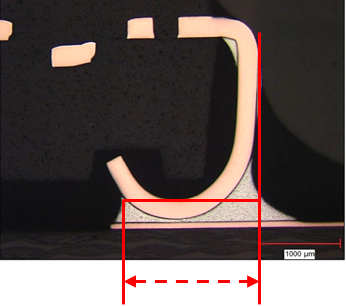

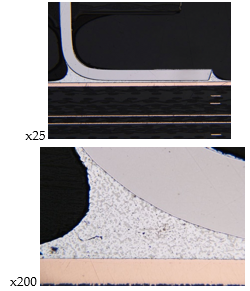

Sculptured flex

ECSS-Q-ST-70-61_1510176Sculptured flex shall be designed in conformance with the requirements of clause 8.7 of ECSS-Q-ST-70-12.

ECSS-Q-ST-70-61_1510177Sculptured flex shall be manufactured and procured according to the requirements of ECSS-Q-ST-70-60.

Printed circuits substrates

Substrates selection

ECSS-Q-ST-70-61_1510178PCBs shall be designed in conformance with the requirements of clause 14 of ECSS-Q-ST-70-12.

ECSS-Q-ST-70-61_1510179PCBs shall be qualified and procured according to the requirements of ECSS-Q-ST-70-60.

ECSS-Q-ST-70-61_1510180Ceramic substrates shall meet the requirements of ECSS-Q-ST-60-05.

Gold finish on PCBs footprint

ECSS-Q-ST-70-61_1510181Degolding of pads shall be performed in accordance with clause 7.6.

RF circuits with gold finishes (see Table 10-13 of ECSS-Q-ST-70-60) can have their pads selectively plated with a tin-lead finish.

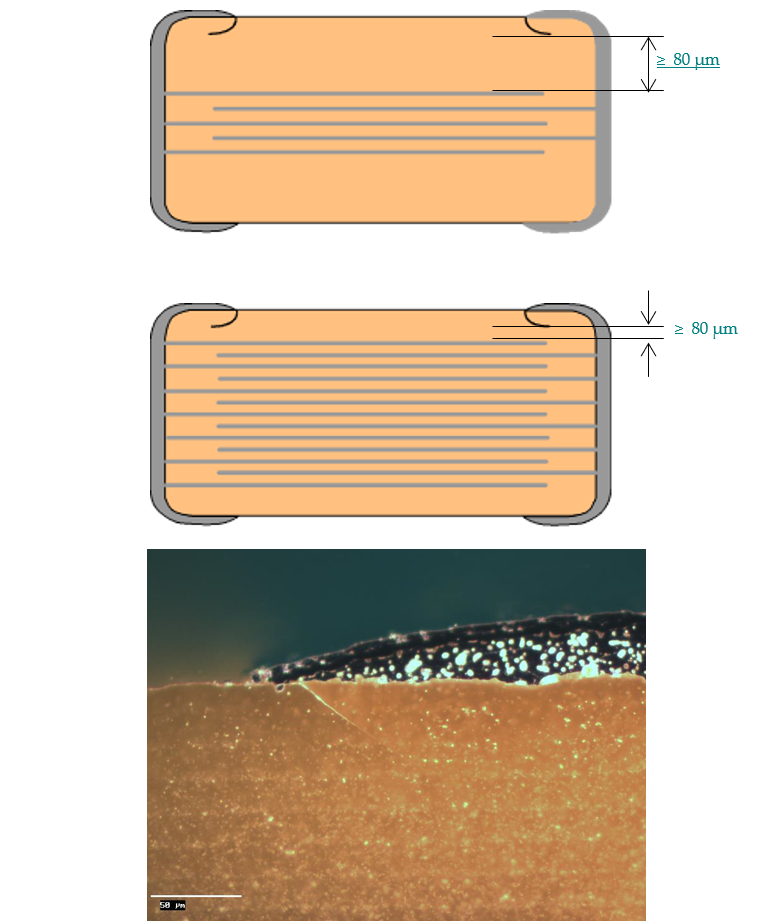

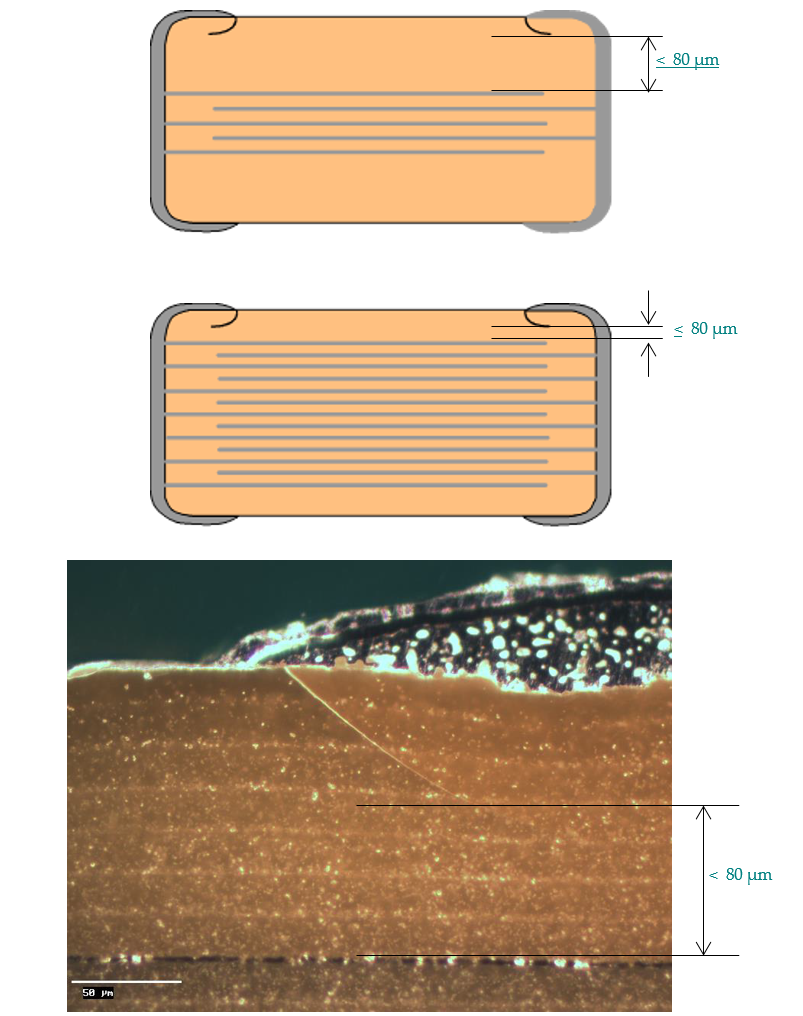

ECSS-Q-ST-70-61_1510182Soldering to gold finish, ENIG, ENIPIG, ENEPIG, qualified according ECSS-Q-ST-70-60, with tin lead may be performed only when the gold finish is thinner than 0,1 μm and is approved by the Approval Authority.

PCB design requirements for wave and selective wave soldering

ECSS-Q-ST-70-61_1510183When wave soldering assembly process is used, PCB design shall be in compliant with requirement 14.3.3f of ECSS-Q-ST-70-12.

ECSS-Q-ST-70-61_1510184The Design constraint specification should at least, include statements about “solder bridging” and “large heat sinks areas.

Proposed statements are:

- “Circuit tracks that are spaced close together should be orientated in line with the pass direction of the solder wave to avoid solder bridging.”

- “Avoid large heat sink areas for ground planes and leads closely connected to massive metal components.”

Components

General

ECSS-Q-ST-70-61_1510185Components termination materials and their finishes shall be selected in compliance with requirements from clause 3 of ESCC23500.

ESCC 23500 is only applicable for procured components and the reprocessing operations as degolding and pretinning are out of its scope.

ECSS-Q-ST-70-61_1510186In case of not golden termination finish, the lead finish shall be checked as per ESCC 25500 in accordance with requirement 4.3.7b.1(f) from ECSS-Q-ST-60.

ECSS-Q-ST-70-61_1510187Components with Silver Palladium finish shall not be used.

ECSS-Q-ST-70-61_1510188Cleaning processes shall not damage the component.

ECSS-Q-ST-70-61_1510189Reprocessing shall not damage the component.

ECSS-Q-ST-70-61_1510190The supplier shall verify, based on the available documentation, that the processing conditions do not exceed the values given by the individual component data sheets.

Examples of processing conditions include maximum temperature to avoid internal melting, thermal shocks, thermal damages, removal of marking ink, degradation of encapsulating plastic.

ECSS-Q-ST-70-61_1510191The supplier may exceed the component manufacturer's mandated processing conditions providing the following conditions are met:

- dedicated tests at component level showing there is no degradation of these components, and

- customer approval.

ECSS-Q-ST-70-61_1510192The plating of the component lead shall be such that the lead forming does not induce any crack in the plating.

ECSS-Q-ST-70-61_1510193When components initially designed for insertion-mount application are used for surface mounting, the assembly shall not damage neither the component, its leads nor the substrate to which it is assembled.

ECSS-Q-ST-70-61_1510194Components to be mounted shall be designed for and be capable of withstanding the soldering temperatures of the particular process being used for fabrication of the assembly.

In case surface mounted components are soldered on both sides of the PCB, double reflow processes can be applied.

Moisture sensitive components

ECSS-Q-ST-70-61_1510195Moisture or process sensitive components as classified by IPC/JEDEC J-STD-020, ECA/IPC/JEDEC J-STD-075 shall be handled in a manner consistent with IPC/JEDEC J-STD-033D.

Any type of plastic encapsulated components with MSL more than 1(one) particularly some plastic BGAs and tantalum capacitors, are moisture sensitive.

ECSS-Q-ST-70-61_1510196When moisture sensitive components are used, bake out shall be performed in accordance with clause 7.4.

Adhesives, potting, underfill and conformal coatings

ECSS-Q-ST-70-61_1510197Adhesives shall be dispensable, non-stringing, and have a reproducible dot volume and shape after application.

ECSS-Q-ST-70-61_1510198Adhesives, pottings, underfill and conformal coatings shall conform to the outgassing requirements of ECSS-Q-ST-70-02.

ECSS-Q-ST-70-61_1510199Materials covered by this clause shall be individually assessed in accordance with clause 4.2.11 and 4.2.15 of ECSS-Q-ST-70-71 when flammability requirements are applicable.

ECSS-Q-ST-70-61_1510200No materials that emit acetic acid, ammonia, amines, hydrochloric acid, and other acids shall be used.

Such compounds can cause stress-corrosion cracking of part leads.

Preparations prior to mounting and soldering

General handling

ECSS-Q-ST-70-61_1510201Operators shall use tools that are fit for the purpose and undamaged prior to use.

ECSS-Q-ST-70-61_1510202ESD-sensitive components shall be handled in accordance with clause 5.4.

ECSS-Q-ST-70-61_1510203During assembly, component termination, terminals, wire ends, and PCB termination areas shall not be touched with bare hands.

ECSS-Q-ST-70-61_1510204After final cleaning, personnel working with PCBs shall wear lint-free gloves or finger cots.

Storage

Components

ECSS-Q-ST-70-61_1510205Storage facilities shall protect components from contaminants and damage.

ECSS-Q-ST-70-61_1510206Storage boxes and bags shall be made of materials which do not degrade the solderability of the components.

ECSS-Q-ST-70-61_1510207Storage materials shall not contain amines, amides, silicones, sulphur, or polysulphides.

ECSS-Q-ST-70-61_1510208Packaging and containers for ESD-sensitive components shall be in accordance with clause 5.4.

PCBs

ECSS-Q-ST-70-61_1510209Bare PCBs shall be stored in accordance with clause 6.12 of ECSS-Q-ST-70-60.

Materials requiring segregation

ECSS-Q-ST-70-61_1510210Solders not in accordance with clause 6.2 shall be removed from the work area.

ECSS-Q-ST-70-61_1510211Activated fluxes shall be stored in accordance with clause 6.3.1c.

Example: ROH1 flux.

ECSS-Q-ST-70-61_1510212Solvents that do not conform to clause 6.4 shall be removed from the work area.

Example: Solvents contaminated with impurities such as inorganic acids.

Baking conditions of PCBs

ECSS-Q-ST-70-61_1510213An oven, as specified in clause 5.5.9, shall be used to bake out PCBs according to requirement 9.2.2a of ECSS-Q-ST-70-60.

ECSS-Q-ST-70-61_1510214Baking of bare PCBs shall be made according to clause 6.12 of ECSS-Q-ST-70-60.

- 1 An alternative good practice to this requirement is: baking for 4 hours at 65 °C in a vacuum oven capable of <50 hPa.

- 2 To prevent delamination of flex material, it is recommended to perform a step baking starting with a low temperature of +80 °C for a minimum of 8 hours and finish at +120 °C for a minimum of 8 hours.

ECSS-Q-ST-70-61_1510215Baking of populated PCBs shall be made when the PCB has been kept under cleanroom conditions for more than 72 hours. - 1 Storage of PCBs in dry cabinet pauses the accumulated clean room storage time.

- 2 A temperature of 80 °C for 4 hours can be sufficient as bake out for populated PCB

ECSS-Q-ST-70-61_1510216Baking of populated PCB shall be made at a temperature which does not degrade the components or assembly.

To limit the bake out operation, which can induce later failure, the PCB can be stored in dry environment after the baking.

Baking and storage of moisture sensitive components

ECSS-Q-ST-70-61_1510217Moisture or process sensitive components, as classified by IPC/JEDEC J-STD-020, and ECA/IPC/JEDEC J-STD-075, shall be stored, handled, and baked consistent with IPC/JEDEC J-STD-033D.

- 1 This is to counteract the “popcorn” effect in soldering using oven or vapor phase reflow techniques.

- 2 Typical baking conditions are from 6 h to 24 h at 125 C depending on the MSL classification, except for components delivered in reels for which a lower temperature and longer time are used.

- 3 It is good practice to store components under nitrogen, dry air (20 % RH maximum) or partial vacuum. This practice does not replace baking when required by MSL classification.

ECSS-Q-ST-70-61_1510218Baking of moisture sensitive components shall be in conformance with manufacturers recommendations.

Preparation of components, wires, terminals, and solder cups

Damage to insulation

ECSS-Q-ST-70-61_1510219The remaining conductor insulation shall not be damaged by the insulation removal process.

ECSS-Q-ST-70-61_1510220Conductors with damaged insulation shall not be used.

- 1 Example: Insulation damage includes nicks, cuts, crushing and charring.

- 2 The operation of mechanical stripping tools can leave slight pressure markings in the remaining conductor insulation. This effect is normal.

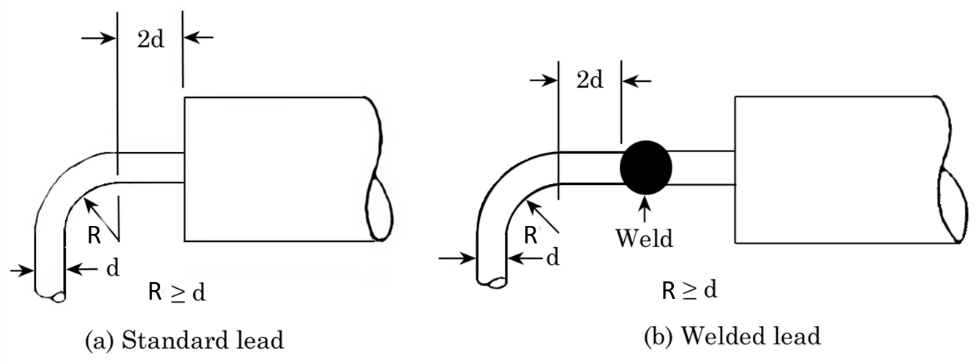

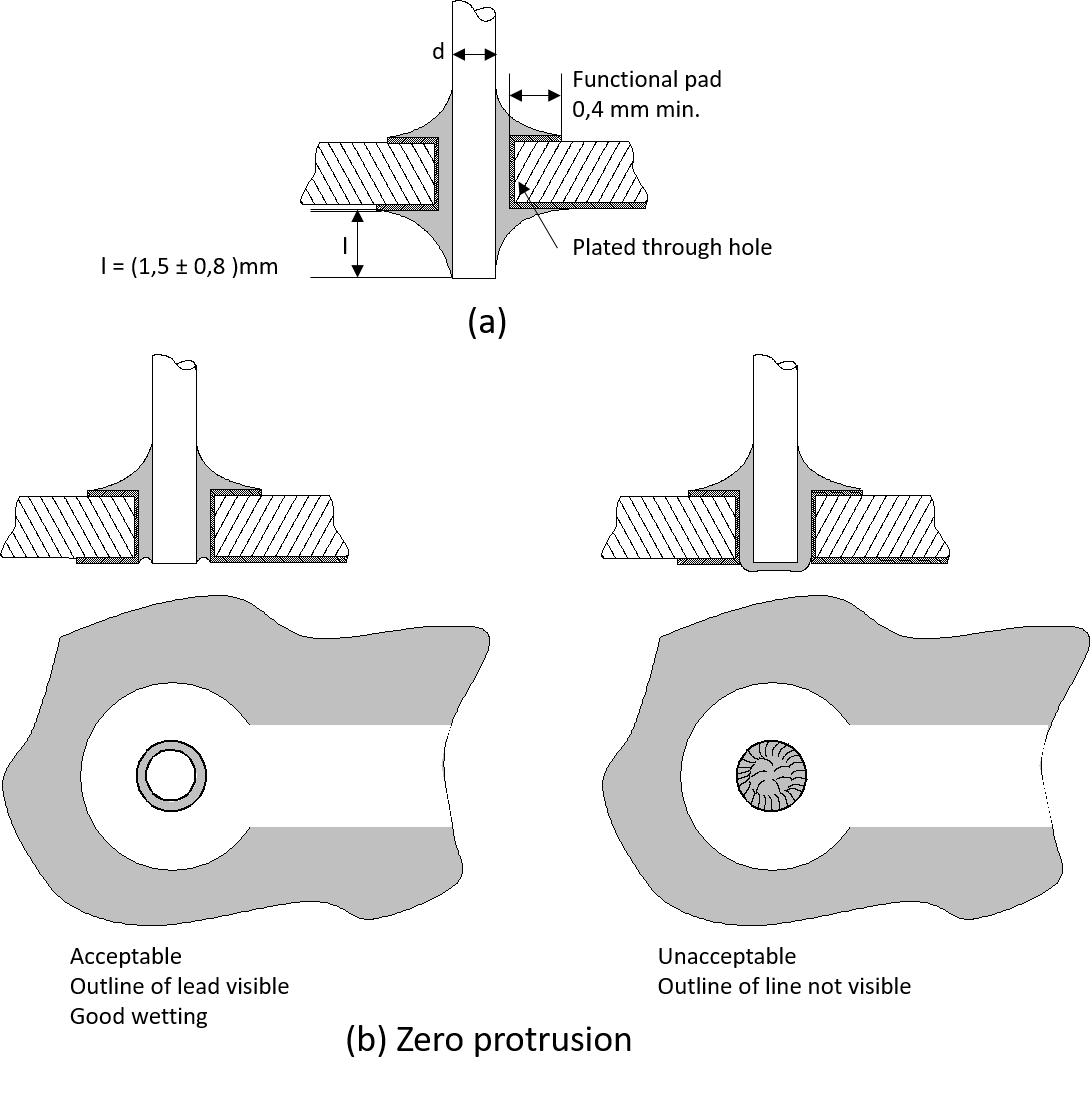

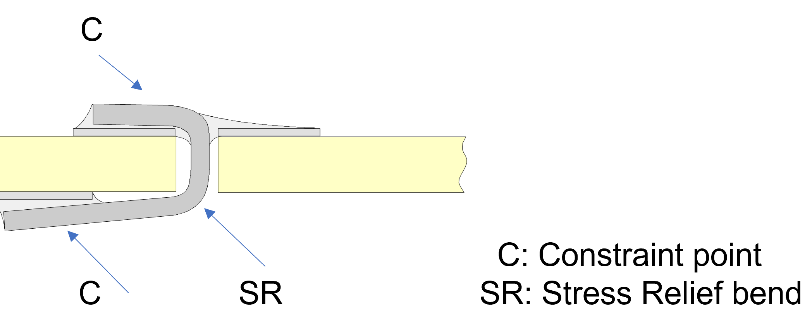

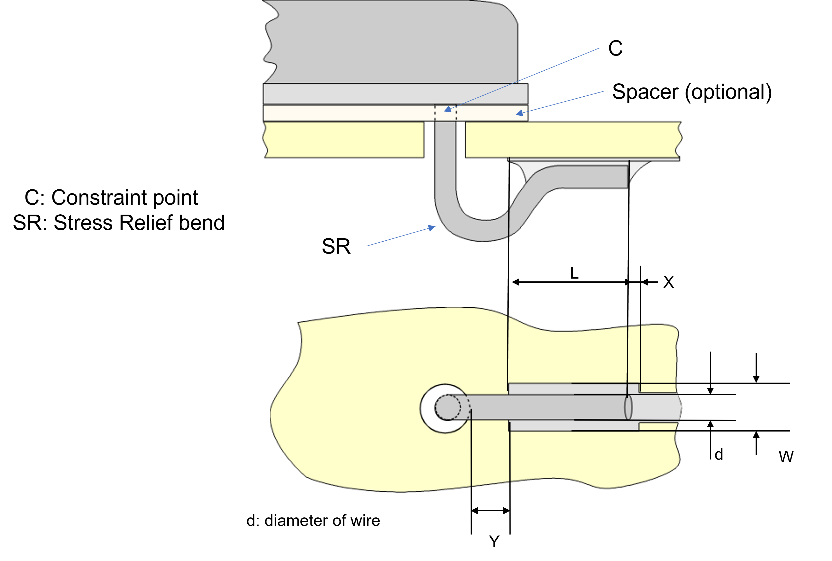

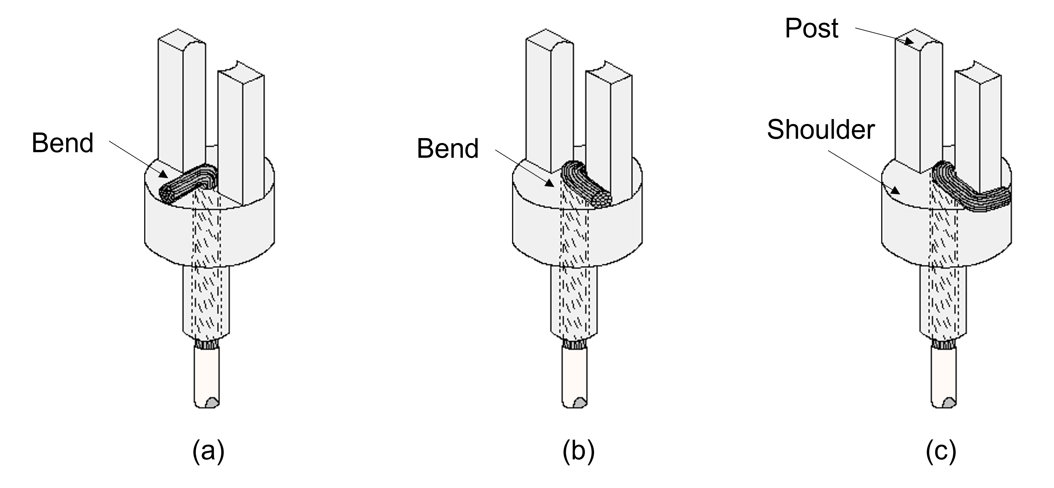

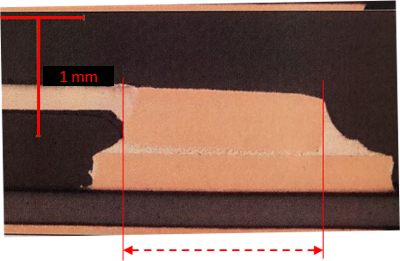

ECSS-Q-ST-70-61_1510221The insulation material shall not be charred by thermal stripping.